ANDやORといった基本ゲートで構成されたネットリストを生成したくて、yosysを試してみました。yosysはフリー(ISC license)のVerilog-HDL合成ツールです。

Veriligで回路設計を行った時、最終的には論理合成ツールでネットリストに変換します。論理合成ツールは、各FPGAメーカーから無償で提供されているものが利用できます。ただ、これらの論理合成ツールは、各FPGAメーカーのデバイスで使用されているLUTを組み合わせたネットリストしか生成できません。yosysでANDやORといった基本ゲートのネットリストが生成できるか試してみました。

インストール

ubuntuの場合は、apt-getでインストールできます。僕はubuntsu14.04LTSの環境にインストールしました。

sudo add-apt-repository ppa:saltmakrell/ppa sudo apt-get update sudo apt-get install yosys

論理合成

合成用のコード

1ビットの加算回路で論理合成を試してみます。正しく合成できれば、XORの等価回路が生成されるはずです。

module add ( in1, in2, out ); input in1; input in2; output out; assign out = in1+in2; endmodule

合成用スクリプト

次のような合成スクリプト(test.ys)を作成します。このスクリプトではtest.vというverilogファイルを読み込み、合成後にsynth.vというファイルを出力しています。

read_verilog test.v hierarchy proc; opt techmap; opt write_verilog synth.v clean

yosysの実行

スクリプトを指定してyosysを実行します。

$yosys test.ys

合成結果

次のようなファイル(synth.v)が生成されます。この段階ではセルライブラリを指定していないので、XOR”^”が合成されています。

(* src = "test.v:1" *) module add(in1, in2, out); (* src = "test.v:6" *) input in1; (* src = "test.v:7" *) input in2; (* src = "test.v:8" *) output out; assign out = in2 ^ in1; endmodule

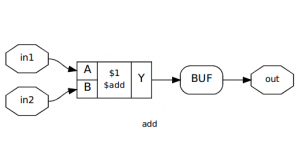

接続関係図の表示

yosysでは、”show”というコマンドで次のような回路図を表示することができます。

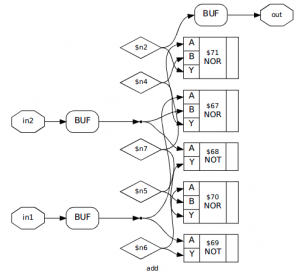

セルライブラリを使った論理合成

論理合成では、通常マッピングするセルライブラリを指定します。ASICなどでは、ベンダーが提供するセルライブラリを使いますが、入手するのが簡単ではありません。適当なセルライブラリが手元に無い場合は、yosysのソースコードに格納されているcmos_cells.libが利用できます。セルライブラリにマッピングする場合のスクリプトは以下です。

read_verilog test.v hierarchy proc; opt techmap; opt abc -liberty cmos_cells.lib write_verilog synth.v clean

セルライブラリを使った論理合成結果

NOTとNORを使ったネットリストが生成されました。

(* src = "test.v:1" *)

module add(in1, in2, out);

wire _00_;

wire _01_;

wire _02_;

wire _03_;

wire _04_;

wire _05_;

wire _06_;

(* src = "test.v:6" *)

input in1;

(* src = "test.v:7" *)

input in2;

(* src = "test.v:8" *)

output out;

NOR _07_ (

.A(_01_),

.B(_00_),

.Y(_03_)

);

NOT _08_ (

.A(_00_),

.Y(_04_)

);

NOT _09_ (

.A(_01_),

.Y(_05_)

);

NOR _10_ (

.A(_05_),

.B(_04_),

.Y(_06_)

);

NOR _11_ (

.A(_06_),

.B(_03_),

.Y(_02_)

);

assign _00_ = in2;

assign _01_ = in1;

assign out = _02_;

endmodule

showで回路図を表示した様子です。ゲートのシンボルは、一般的なものとは少し違っています。

まとめ

yosysはまだ開発中のようですが(試したのはRelease 0.5)、基本的な論理合成は問題なく実行できました。次はクロックを使った同期回路を試してみたいと思います。