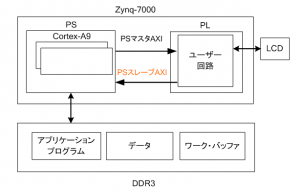

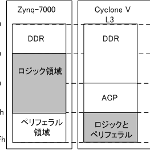

Zynq-7000のPL(Programmable Logic)にAXIマスタのユーザー回路を実装した場合、その接続先はPS(Processing System)のAXIスレーブ・インターフェースです。例えば、ユーザー回路からメイン・メモリをアクセスしたい場合にはこのような構成になります。

このとき、AXIスレーブは次の3種類から選べます。

- S_AXI_GP: 汎用

- S_AXI_HP: ハイ・パフォーマンス用

- S_AXI_ACP: CPUとキャッシュ・コヒーレント

では、同一のユーザー回路を3種類のAXIスレーブに接続した場合、その種類によって「AXIの応答に違いはあるのか」を実験で確認してみました。

AXIスレーブの応答比較

3種類のAXIスレーブ

Zynq-7000の仕様書によると、各インターフェースには次のような特徴があります。

| インターフェース名 | ビット幅 | 最大クロック周波数 | R/Wバンド幅 | I/F数 |

| S_AXI_GP | 32 | 150MHz | 1200Byte/Sec. | 2 |

| S_AXI_HP | 64/32 | 150MHz | 2400/1200Byte/Sec. | 4 |

| S_AXI_ACP | 64 | 150MHz | 2400Byte/Sec. | 1 |

動作確認用ユーザー回路

次のような画像処理システムを、ユーザー回路としてPLに実装しました。ユーザー回路の動作周波数は50MHzです。

AXIスレーブを実験するユーザー回路

計測方法

AXI応答の計測は、PL内部に実装した計測用の回路で行いました。計測内容は、リードチャネルで3種類、ライトチャネルで3種類の合わせて6種類の項目を計測しました。

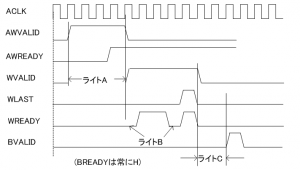

ライトチャネルの計測

| 項目 | 名称 | 説明 |

| ライトA | ライト・コマンドの受付サイクル数 | AWVALID=HからAWREADY=Hまでのサイクル数 |

| ライトB | ライト・データの受付不可サイクル数 | バースト長分のWVALID=H出力時のWREADY=Lのサイクル数 |

| ライトC | ライト・レスポンスのレイテンシ | WLAST=HのデータからBVALID=Hまでのサイクル数 |

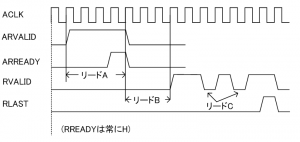

リードチャネルの計測

| 項目 | 名称 | 説明 |

| リードA | リード・コマンドの受付サイクル数 | ARVALID=HからARREADY=Hまでのサイクル数 |

| リードB | リード・データの初期レイテンシ | リード・コマンド受付から先頭データ(RVALID=H)までのサイクル数 |

| リードC | リード・データの無効サイクル数 | 先頭データからバースト長分のデータをリードするまでの無効サイクル数(RVALID=Lのサイクル数) |

計測結果

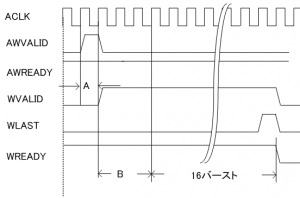

AXIスレーブは3種類ですが、S_AXI_HPはデータ・バス幅として32ビットまたは64ビットが選択できるので、合計4種類のAXIスレーブについて計測を行いました(AXIの32/64データ・バス幅の対応はユーザー回路側で行っています)。

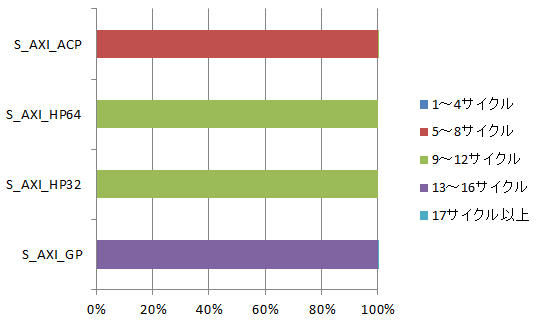

ライトチャネル

ライトAとライトBは、すべてが同じ応答でした。

具体的にはライトAはすべて1サイクル、またライトBはすべて0サイクルでした。つまり、ライト・コマンドとライト・データは、すべてウェイトなしでAXIインターフェースに送出されました。応答タイミングに違いがないということは、データ・バス幅を32ビットから64ビット化することで、実際に2倍のデータを同一タイミングで転送できそうです。ライト・チャネルについて、唯一違いが見られたのがライトCのレスポンス・レイテンシです。

WLAST受付からBVALIDが戻ってくるまでのサイクルは、S_AXI_ACPが5~8サイクル、S_AXH_HP64/32が9~12サイクル、S_AXI_GP32が13~16サイクルでした。

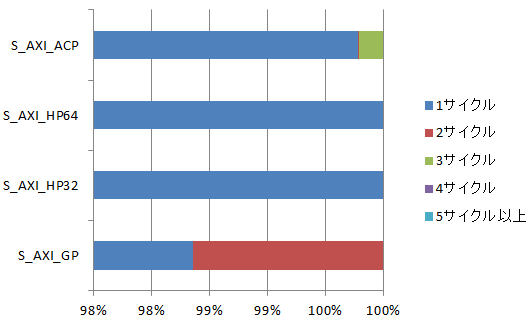

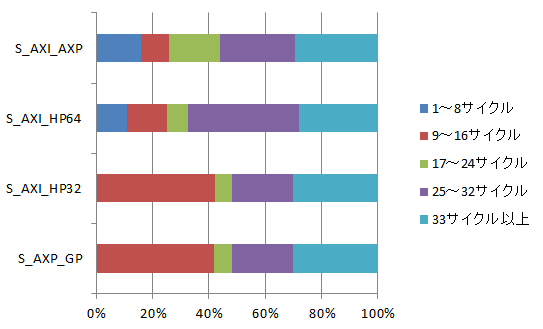

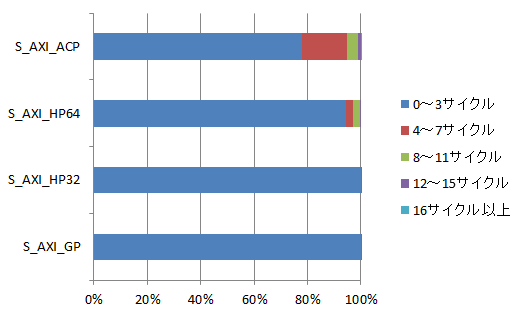

リードチャネル

リード・チャネルは、32ビットと64ビットのAXIで応答に違いが見られました。

ほとんどのリード・コマンドは1サイクルで受け付けられました。S_AXI_GPやS_AXI_ACPでは2~3サイクル後のコマンド受付も計測されましたが、全体の1%以下でした。次に、リードBの計測結果です。

同じデータ・バス幅のAXIスレーブは似た傾向の結果になりました。32ビットのS_AXI_HP32とS_AXI_GPは、一番低レイテンシが9~16サイクルで全体の約40%、高レイテンシの33サイクル以上が約30%という分布でした。64ビットのS_AXI_HP64とS_AXI_ACPは、1~8サイクルという低レイテンシのメモリ・リードも計測されました。最後に、リードCの計測結果です。

1回のリード・コマンドの応答として帰ってくるリード・データについて、無効サイクルはほとんどの場合に0~3サイクルでした。無効サイクルについては、64ビット系システムの方が32ビットシステムよりも多いという結果でした。特に、S_AXI_ACPは、約20%は無効サイクルが4サイクル以上でした。

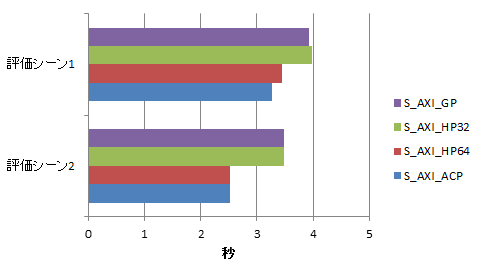

描画時間

このユーザー回路は画像表示システムなので、描画速度の比較も行いました。描画速度の速い順に次のようになりました。

- S_AXI_ACP

- S_AXI_HP64

- S_AXI_GP

- S_AXI_HP32

AXIのバス幅が32ビットと64ビットの場合を比べると、64ビットの方が20~30%高速でした。32ビット同士を比較した場合、S_AXI_HP32よりもS_AXI_GPの方がわずかに高速という興味深い結果になりました。

まとめ

S_AXI_HPとS_AXI_ACPは、応答にもう少し違いが出ると予想していたのですが、あまり大きな違いはありませんでした。今回のユーザー回路は画像表示系なので、キャッシュ・フラッシュの頻度があまり高くありません(1/60秒に1回程度)。Zynq-7000の仕様書にも、キャッシュ・フラッシュの頻度がこの程度の場合には、あまりACPは効果的ではないと記載があるので、仕様書に記載されている通りの結果ともいえます。