FPGA

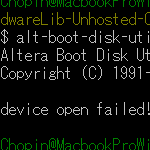

FPGA Altera Boot Disk Utilityのエラー

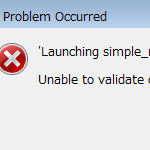

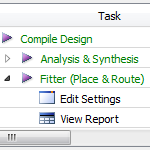

Cyclone Vでベアメタルアプリ(bare metal: LinuxなどのOSを使わないアプリ)を作成する場合、アプリのバイナリをalt-boot-disk-utilでSDカードにコピーします。 ベアメタルアプリ作成の詳しい手順はこちら...

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA