設計

設計 doxverilogのインストール

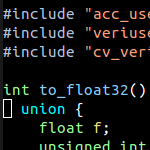

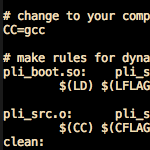

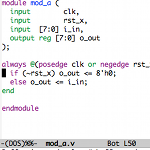

Verilog用のドキュメントジェネレータdoxverilogをインストールして試しました。SourceForgeのダウンロードデータが壊れているので、インストールにかなり苦戦しました。 doxverilogについて doxverilogは...

設計

設計  設計

設計  OpenCores

OpenCores  OpenCores

OpenCores  OpenCores

OpenCores  設計

設計  設計

設計  設計

設計  設計

設計  設計

設計