設計

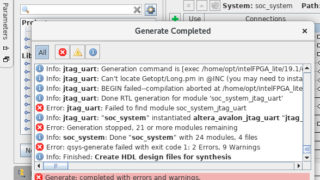

設計 Quartus Prime 19.1のPlatform DesignerでGenerateが失敗する

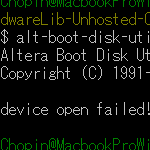

Quartus Prime ライト・エディションのバージョン19.1からPlatform Designerを起動し、GenerateでHDLを生成しようとすると、次のようなエラーが発生しました。 Quartus Primeの実行プラットフォ...

設計

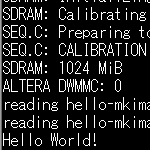

設計  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  開発キット

開発キット