FPGA

FPGA ISE14.7 for Windows10のインストール

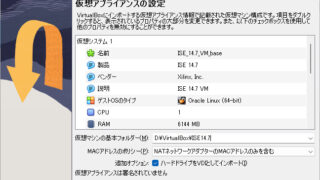

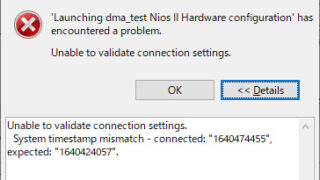

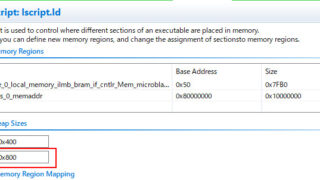

Spartan3やSpartan6のような古いFPGAを搭載した開発キットの動作確認を行うためにISE14.7 for Windows10をインストールしようとした所、次のようなエラーが発生しました。 ISE14.7 for Windows...

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA