VivadoのAXI Verification IP(AXI VIP)をWindows10のコマンドプロンプトから実行したときのメモです。

サンプルの生成

Vivadoで適当なプロジェクトを作成してIP CatalogからAXI VIPを生成します。次にSourcesタブでIPを右クリックして表示されるメニューからOpen IP Example Design…を選ぶとAXI VIPのサンプルプロジェクトが生成されます。 このサンプルプロジェクトを参考に実行環境を作成します。

バッチファイルの用意

シミュレーション用のバッチファイルを作成します。バッチファイルでは、xvlog, xelab, xsimを順に実行します。トップモジュール名はtopです。

// sim.bat

call xvlog --incr --relax -L uvm -L axi_vip_v1_1_8 -L xilinx_vip -prj spi.prj

call xelab xil_defaultlib.top --incr --debug typical --relax --mt 2 -L xil_defaultlib -L axi_infrastructure_v1_1_0 -L axi_vip_v1_1_8 -L uvm -L xilinx_vip --snapshot xil_defaultlib.top

call xsim xil_defaultlib.top -tclbatch spi.tclxvlogで読み込んでいるspi.prjには、コンパイル対象のファイルを記述します。AXI マスターのVIPのみを使用する場合、必要なファイルは ex_sim_axi_vip_mst_0_pkg.sv と ex_sim_axi_vip_mst_0.sv です。

// spi.prj

sv xil_defaultlib -i "../../../../imports" \

"./vip/ex_sim_axi_vip_mst_0/sim/ex_sim_axi_vip_mst_0_pkg.sv" \

"./vip/ex_sim_axi_vip_mst_0/sim/ex_sim_axi_vip_mst_0.sv" \

verilog xil_defaultlib -i "../include" --include "../opencores/rtl/verilog" \

"../opencores/rtl/verilog/spi_top.v" \

"../opencores/rtl/verilog/spi_shift.v" \

"../opencores/rtl/verilog/spi_clgen.v" \

"../rtl/fm_axi_s.v" \

"../rtl/fm_fifo.v" \

"../rtl/spi_oc.v" \

"../scenario/dut.v" \

sv xil_defaultlib -i "../../../../imports"\

"../scenario/test.sv" \

nosort

xsim用のtclスクリプトを用意します。xsimを実行して終了するたけのスクリプトです。

// spi.tcl

run -all

exit

テストシナリオ

サンプルで生成されるaxi_vip_0_mst_stimulus.svhを参考にテストシナリオを作成します。単純なAXIのリードとライトは、ファイル内で定義されているsingle_write_transaction_apiと single_read_transaction_apiの2つのtaskで生成できます。

//axi_vip_0_mst_stimulus.svh

import axi_vip_pkg::*;

import ex_sim_axi_vip_mst_0_pkg::*;

ex_sim_axi_vip_mst_0_mst_t mst_agent;

task mst_start_stimulus();

mst_agent = new("master vip agent",DUT.axi_vip_mst.inst.IF);

mst_agent.start_master();

// single write transaction

mtestWID = $urandom_range(0,(1<<(0)-1));

mtestWADDR = 0;

mtestWBurstLength = 0;

mtestWDataSize = xil_axi_size_t'(xil_clog2((32)/8));

mtestWBurstType = XIL_AXI_BURST_TYPE_INCR;

mtestWData = $urandom();

single_write_transaction_api("single write with api",

.id(mtestWID),

.addr(mtestWADDR),

.len(mtestWBurstLength),

.size(mtestWDataSize),

.burst(mtestWBurstType),

.wuser(mtestWUSER),

.awuser(mtestAWUSER),

.data(mtestWData)

);

//single read transaction

mtestRID = $urandom_range(0,(1<<(0)-1));

mtestRADDR = $urandom_range(0,(1<<(32)-1));

mtestRBurstLength = 0;

mtestRDataSize = xil_axi_size_t'(xil_clog2((32)/8));

mtestRBurstType = XIL_AXI_BURST_TYPE_INCR;

single_read_transaction_api("single read with api",

.id(mtestRID),

.addr(mtestRADDR),

.len(mtestRBurstLength),

.size(mtestRDataSize),

.burst(mtestRBurstType)

);

endtaskテストベンチのトップモジュール

シミュレーション用のトップモジュールでは、クロックとリセットを生成します。また、AXI VIPのテストシナリオをincludeして、実行するトランザクションを記述したtaskをinitial文で呼び出します。

// test.sv

`timescale 1ns/1ns

import axi_vip_pkg::*;

module top;

bit clk;

bit rst_x;

`include "axi_vip_0_mst_stimulus.svh"

dut DUT(

.aresetn(rst_x),

.aclk(clk)

);

initial begin

clk = 1;

forever begin

#5 clk = ~clk;

end

end

initial begin

$dumpvars;

rst_x = 1;

@(negedge clk);

@(negedge clk);

rst_x = 0;

@(negedge clk);

@(negedge clk);

rst_x = 1;

@(negedge clk);

end

initial begin

repeat (10) @(posedge clk);

fork

mst_start_stimulus();

join;

repeat (1000) @(posedge clk);

$finish;

end

endmodule

シミュレーション実行

コマンドプロンプトを開いて、Vivadoのインストールディレクトリに格納されているsettings64.batを実行します。その後、sim.batが存在するディレクトリに移動してsim.batを実行するとシミュレーションが始まります。実行時、AXIのプロトコルに問題があれば、ワーニングやエラーが表示されます。

XilinxAXIVIP: Found at Path: top.DUT.axi_vip_mst.inst

Error: Pre-reset violation: AXI4_ERRS_AWREADY_X: When not in reset, a value of X on AWREADY is not permitted. Spec: section A3.1.2.

ERROR: 40 ns top.DUT.axi_vip_mst.inst.IF : XILINX_RESET_PULSE_WIDTH: Holding AXI ARESETN asserted for 16 cycles of the slowest AXI clock is generally a sufficient reset pulse width for Xilinx IP. --UG1037. To downgrade, use <hierarchy_path to VIP>.IF.set_xilinx_reset_check_to_warn(), or filter using clr_xilinx_reset_check().

essfully

Executing Axi4 End Of Simulation checks

$finish called at time : xx ns

## exit

INFO: [Common 17-206] Exiting xsim at ...

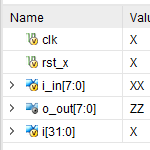

テストベンチでvcdを生成すれば波形を確認できます。