開発キット

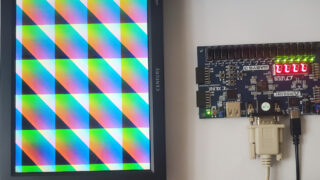

開発キット Basys 3の動作確認

動作確認のために、公式サイトのサンプルプロジェクトをVivadoでビルドしたときのメモです。Basys 3の公式マニュアルとサンプルプロジェクトBasys 3の公式資料等は次のとおりです。Basys 3Basys 3 Reference M...

開発キット

開発キット  開発キット

開発キット  開発キット

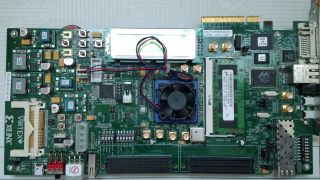

開発キット  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

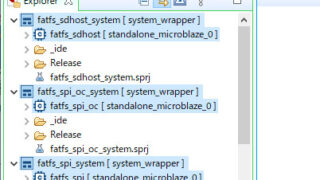

FPGA  設計

設計  設計

設計  設計

設計