設計

設計 [DRC NSTD-1]と[DRC UCIO-1]のエラー

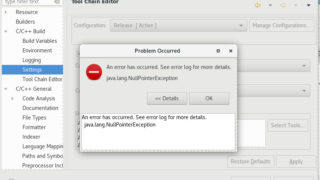

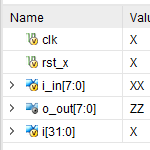

昔のArty用VivadoプロジェクトデータをVivado2017.2でビルドすると、bitgenで次のエラーが発生しました。[DRC NSTD-1] Unspecified I/O Standard: 4 out of 66 logica...

設計

設計  設計

設計  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA