Tclスクリプトを使ったVivadoのコマンドライン実行は非常に快適なのですが、唯一困るのがロジックアナライザの設定です。ロジックアナライザを利用する場合は、追加の処理が必要になります。

Tclスクリプトとロジックアナライザの設定

前提

VivadoのTclスクリプトは、各フェーズで分割されているとします。具体的には、次のような分割です。

| ファイル名 | 内容 |

| ip.tcl | IP Integrator用Tclスクリプト |

| synth.tcl | 合成用Tclスクリプト |

| implement.tcl | インプリメンテーション用Tclスクリプト |

| bitgen.tcl | ビットデータ生成用Tclスクリプト |

| load_fpga.tcl | ビットデータロード用Tclスクリプト |

| launch_sdk.tcl | SDK起動用Tclスクリプト |

前処理

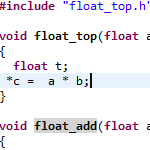

ロジックアナライザで観測する信号を設定します。例えば、RTL中にmark_debugなどで観測する信号を指定します(これは、Tclスクリプトで処理をするかどうかに関係ありませんが)。

(* mark_debug = "true" *) output o_awvalid_m;

論理合成

synth.tclを使って論理合成を実行します。

vivado -m64 -mode batch -source synth.tcl

この例では、論理合成の結果は、synth.tcl内に記述されたwrite_checkpointコマンドによって、zed_base_wrapper.dcpという名前のファイルに格納されているとします。

ロジックアナライザの挿入

Vivado GUIを使って、ロジックアナライザに関する情報を挿入します。

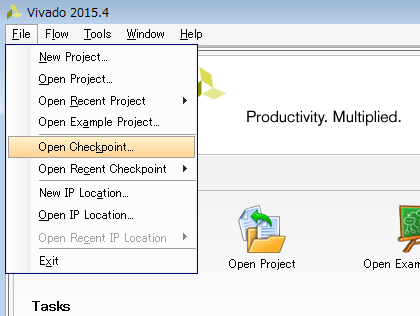

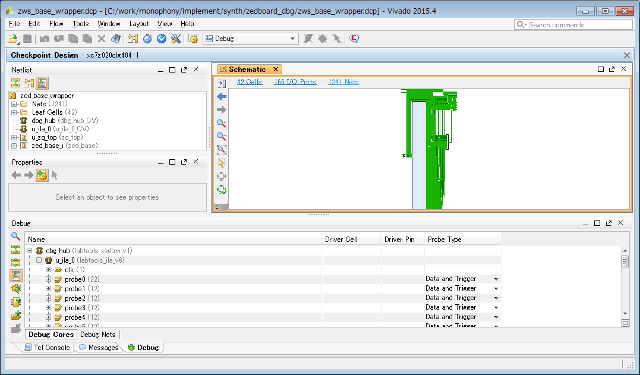

まず、VivadoのGUIを起動します。そして、File->Open Checkpoint…からzed_base_wrapper.dcpを読み込みます。

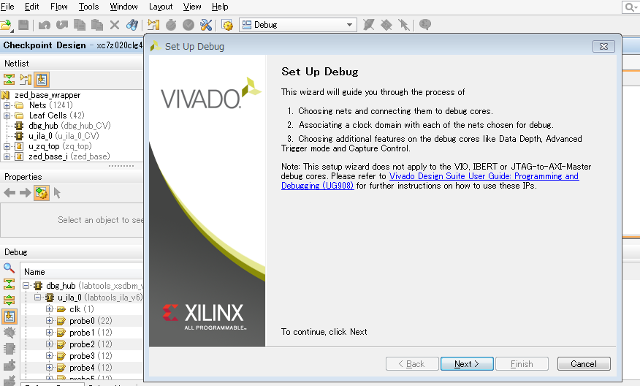

Tools->Set Up Debug…ウィザードでロジックアナライザを挿入します(詳しい手順はこちら)。

次に、Tcl Consoleタブを選択して、write_checkpoint -forceでcheckpointを上書きします。

write_checkpoint -force zed_base_wrapper.dcp

ここで、-forceを付けないと、次のようなエラーが発生します。

ERROR: [Common 17-176] Overwrite of existing file isn't enabled. Please specify -force to overwrite file [C:zedboard_dbg/zed_base_wrapper.dcp]

逆に考えれば、-forceなしでエラーが出るということは「正しく上書きされようとしている」ということです。正しくzed_base_wrapper.dcpを上書きできれば、ここでVivadoを一旦終了します。

配置配線

Tclスクリプトを使って、配置配線を実行します。Tclスクリプトに特に変更は必要ありません。

vivado -m64 -mode batch -source implement.tcl

bitstreamの生成

ロジックアナライザを利用するには、write_debug_probesコマンドで.ltxファイルを生成する必要があります。具体的には、bitstreamを生成するTclファイルにwrite_debug_probesコマンドを追加します。

set PROJ_NAME polyphony

set PROJ_DIR .

set SDK_DIR ./sdk

set TOP_NAME zed_base_wrapper

open_checkpoint ${TOP_NAME}_routed.dcp

write_bitstream -verbose -force ${TOP_NAME}.bit

write_sysdef -force -hwdef ${TOP_NAME}.hwdef -bitfile ${TOP_NAME}.bit -meminfo ${TOP_NAME}.mmi -file ${TOP_NAME}.sysdef

write_debug_probes -force ${TOP_NAME}.ltx # これを追加

file copy -force ${TOP_NAME}.sysdef ${SDK_DIR}/${TOP_NAME}.hdf

write_debug_probesを追加後、TclスクリプトをVivadoで実行します。

vivado -m64 -mode batch -source bitgen.tcl

Vivadoロジックアナライザの起動

簡単なVivadoプロジェクトを作成してVivado GUIを起動します。簡単なプロジェクトは、例えば次のようなTclスクリプトで生成できます。

set PROJ_NAME test_prj

create_project -verbose -force -part xc7z020clg484-1 ${PROJ_NAME}

set_property board_part em.avnet.com:zed:part0:1.3 [current_project]

close_project

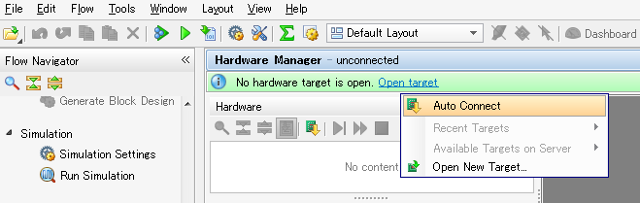

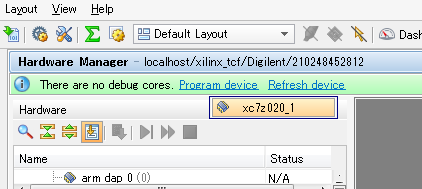

Vivaoを起動して、Open Project…でプロジェクトを読み込みます。次に、Flow NavigatorのProgram and DebugからOpen Targetを選択し、Auto Connectでターゲットボードと接続します。

次に、Program Deviceを実行します。

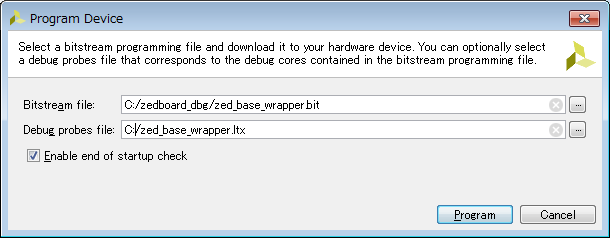

この時に表示されるポップアップウィンドウに、bitstreamとwrite_debug_probesで生成した.ltxファイルを指定して、Programをクリックします。

この後の処理は、通常の手順と同じです。

まとめ

まとめると、ロジックアナライザを利用するために追加で必要になる処理は次の2点です。

- 論理合成後のcheckpointをVivado GUIで読み込んで、ロジックアナライザの情報を組み込んでからwrite_checkpointで上書きする。

- write_debug_probesで.ltxファイルを生成する。