Xilinx社の最新の開発環境はVivadoに移行しましたが、Virtex-6やSpartan-6、またそれらよりも古いデバイスを使う場合は、以前の開発環境であるISEを使うことになります。

ISEでは、CORE Generatorをつかって、IPコアの生成が行えます。例えば、DDR用IPコアのmigやソフトコア・プロセッサのMicroBlaze MCSはCORE Generatorで生成できます。CORE GeneratorはデフォルトでGUIが起動しますが、バッチ形式でコマンドラインから実行することも可能です。バッチ形式で実行する場合の手順は次のとおりです。

CORE Generatorをコマンドラインから実行する手順

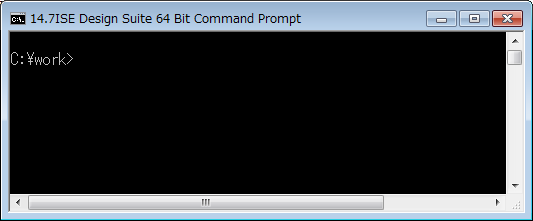

まず、ISEのコマンドプロンプトを起動します。Windowsの場合は、Xilinx Design Tools->ISE Design Suite 14.x->Accessories->ISE Design Suite 64(or32) Bit Command Promptで起動します。Linuxの場合は、ターミナルを起動してから、ISEインストールディレクトリにあるsetting32/64.shまたはsetting32/64.cshをsourceします。

1. GUIでプロジェクトを作成してIPコアを登録する

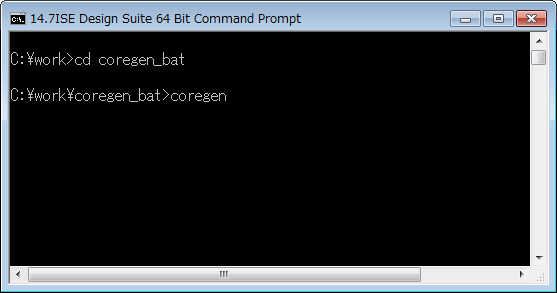

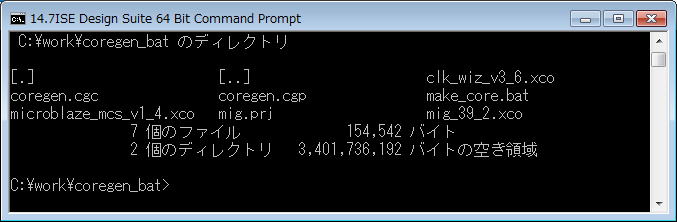

IPコアを生成するディレクトリを作成し、ISEコマンドプロンプトのカレント・ディレクトリをそこに移動します。この例では、C:\work\coregen_batに移動しています。

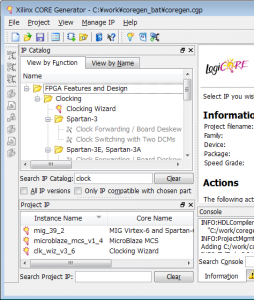

次に、通常の手順でCORE Generatorのプロジェクトを作成し、適切なパラメータを設定してIPコアを生成します。この例では、mig, microblaze_mcs, clk_wizをIPコアとして生成しています。

2. 不要なファイルを削除する

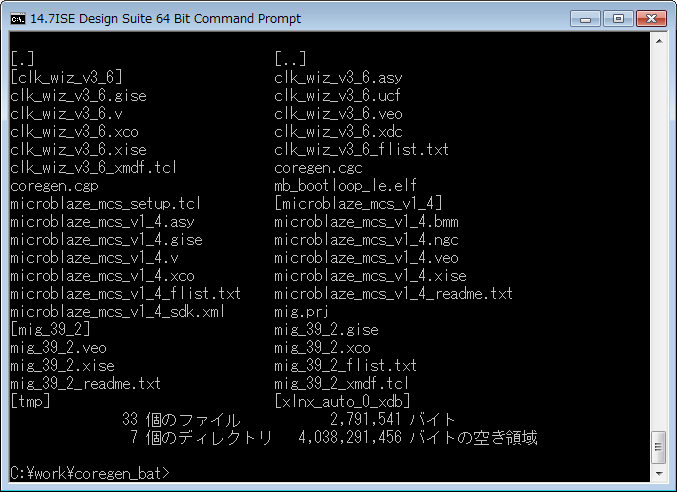

GUIを使ってCORE GeneratorからIPコアを生成したとき、ディレクトリには次のようなファイルが生成されています。

これらのファイルから、IPコアの生成に必要な最低限のファイルを除いて削除します。具体的には、拡張子が.cgc,.cgp,.xco,.prjのファイルを残し、それ以外のファイルをすべて削除します。

4. ファイルの修正

IPコアによっては、.xcoファイルの修正が必要です。例えばmigは、次のようにmig.prjの参照ディレクトリをカレント・ディレクトリに修正する必要があります。

#CSET xml_input_file=./mig_39_2/user_design/mig.prj CSET xml_input_file=./mig.prj

5. バッチファイルの作成

次のようなバッチファイル(Linuxの場合はシェル・スクリプト)を作成します。coregenの-bオプションで.xcoを指定し、-pオプションで.cgpを指定します。

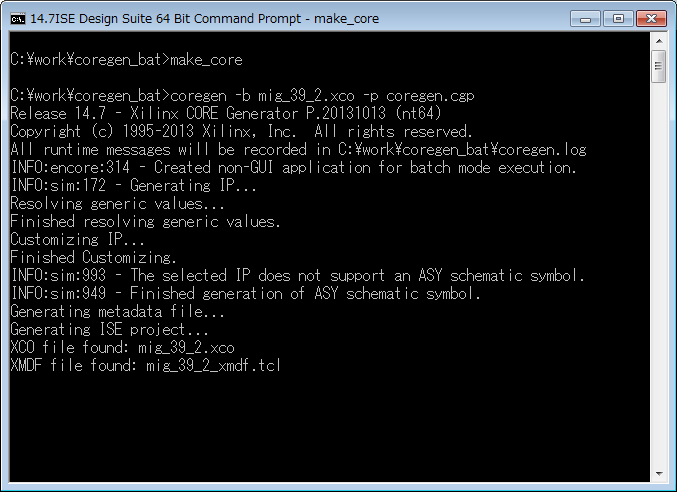

coregen -b coregen -b mig_39_2.xco -p coregen.cgp microblaze_mcs_v1_4.xco -p coregen.cgp coregen -b clk_wiz_v3_6.xco -p coregen.cgp

6. IPコアの生成確認

コマンドプロンプトからmake_core.batを実行します。

まとめ

このように、IPコアの生成に必要な最低限の設定ファイルだけを残しておけば、必要なときにコマンドラインから一発でIPコアのHDLファイルを生成することができます。