xstはISE標準の論理合成ツールです。論理合成可能なVerilogやVHDLのコードをネットリストに変換します。VerilogのサポートはVerilog2001です。SystemVerilogはサポートされていません。

xstをコマンドラインから実行する

設定ファイル

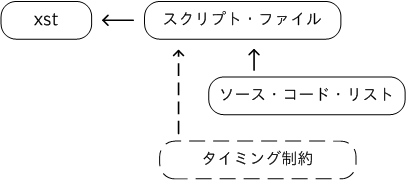

xstをコマンドラインから実行する場合、最低限2つのファイルが必要になります。1つはスクリプト・ファイル、もう1つはソース・コード・リストのファイルです。スクリプト・ファイルには、FPGAデバイスの情報や論理合成のオプションを列挙します。ソース・コード・リストには、論理合成を行うHDLを記述したファイル名を記述します。ソース・コード・リストのファイル名は、スクリプト・ファイル内で指定します。クロック等のタイミング制約が必要な場合は、その設定を記述したファイルを作成し、スクリプト・ファイル内でそのファイル名を指定します。

スクリプト・ファイルの例

スクリプト・ファイルは、次のようなテキストファイルです。

# xst script

run

-p xc3s1500fg456-4

-opt_mode Speed

-rtlview yes

-keep_hierarchy yes

#-uc pp_top.xcf

-resource_sharing no

-register_balancing yes

-keep_hierarchy no

-opt_level 2

-ifn rtl_files.prj

# -ifmt mixed

-ifmt verilog

-top pp_top

-iobuf yes

-ofn ./pp_top.ngc

-define {PSOC_IN}

-vlgincdir {../rtl/fm_sdr ../rtl/fm_3d ../rtl/fm_pci}

-sd {}

通常、最初にrunを書き、続いてオプションを列挙します。#の行はコメントです。良く使うオプションは次のとおりです。

-p

論理合成対象のFPGAデバイスを指定します。この例ではSpartan-3(xc3s1500fg456-4)を指定しています。

-opt_mode

論理合成をスピード優先(speed)にするか、サイズ優先(area)にするかを指定します。最適化レベルは-opt_levelを1か2で指定します。デフォルトはSpeedです。

-keep_hierarchy

論理合成時、RTLの階層構造を保持するかどうかをyes/noで指定します。階層構造を破壊した方が、最適化された回路が生成される場合があります。デバッグ時は、階層構造を保持した方が解析が楽です。

-ifn

ソース・コードのリストを記述したファイルを指定します。Verilogの場合、ファイルのパスをincludeで指定します。VHDLやVerilog/VHDL混合の場合はveirlog workというフォーマットでパスを指定します。

// verilog files `include "../rtl/fm_sh4/fm_sh4.v" `include "../rtl/fm_sh4/fm_dispatch.v" `include "../rtl/fm_sh4/fm_dispatch_dma.v" `include "../rtl/fm_sys/fm_sys" // in mixed mode, `include -> verilog work

-ifmt

ソース・コードの言語をverilogまたはvhdlで指定します。VerilogとVHDLを混合する場合はmixedを指定します。

-top

最上位のモジュール名を指定します。この例ではpp_topです。

-iobuf

I/Oバッファを使用するかどうかをyes/noで指定します。内部モジュールを論理合成する場合には、noを指定する必要があります。デフォルトはyesです。

-ofn

論理合成結果を格納するファイルを指定します。この例ではpp_top.ngcです。

-define

Verilogのdefineを設定します。この例ではPSOC_INをdefineしています。defineが複数必要な場合は、{}で囲んで列挙します。defineは、Verilogコード中のifdefを確定するために必要になります。

-vlgincdir

Verilogのincludeがサーチするパスを指定します。 複数のパスが必要な場合は、{}で囲んで列挙します。

-sd

合成済みのモジュール等をリンクする場合のパスを指定します。xstでリンクしない場合は、ngdbuildでもリンクできます。

実行方法

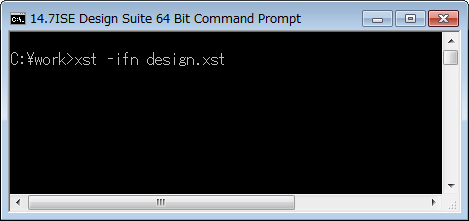

ISEコマンドプロンプトなどから-ifnオプションでスクリプト・ファイルを指定してxstを実行します。

実行結果

xstの実行プロセスはログ(.srp)に記録されます。ログの内容を見ると、指定したオプションが実際に認識されているかどうかを確認できます。

=========================================================================

* Synthesis Options Summary *

=========================================================================

---- Source Parameters

Input File Name : "rtl_files.prj"

Input Format : verilog

Verilog Include Directory : {../rtl/fm_sdr ../rtl/fm_3d ../rtl/fm_pci}

---- Target Parameters

Target Device : xc3s1500fg456-4

Output File Name : "./pp_top.ngc"

Output Format : NGC

---- Source Options

Resource Sharing : no

Automatic Register Balancing : yes

Top Module Name : pp_top

Verilog Macros : {PSOC_IN}

---- General Options

Optimization Goal : Speed

RTL Output : yes

Keep Hierarchy : yes

Optimization Effort : 2

---- Other Options

Cores Search Directories : {}

verilogネットリストの生成

論理合成の結果は、.ngcファイルにNGCフォーマットで格納されますが、netgenを使うとVerilogフォーマットのネットリストを生成できます。このネットリストとVerilogシミュレータでゲートレベルのシミュレーションを実行できます。

netgen -sim -ofmt verilog -w pp_top.ngc

まとめ

xstにはいろいろな設定がありますが、デフォルト設定がベストな結果を出す場合が多い気がします(xstに限らず、ISE全般で)。最終的な結果はmapやparを使った配置配線に依存するので、個人的にはxstの結果は目安程度にしか考えていません。