古いZyboの動作確認のために、公式サイトのサンプルプロジェクトをビルドしたときのメモです。

Zyboの公式マニュアルとサンプルプロジェクト

Zybo Zynq-7000 の公式資料等は次のとおりですが、生産が終了しているため一部にリンク切れが見られます。

サンプルプロジェクトは次の4種類が用意されています。

4つ用意されているサンプルプロジェクトの中で、現在もダウンロード可能であり、かつ動作が視覚的にわかりやすいHDMI Output Demoをビルドして実行します。

サンプルデータの実行

Vivado2016.4のインストール

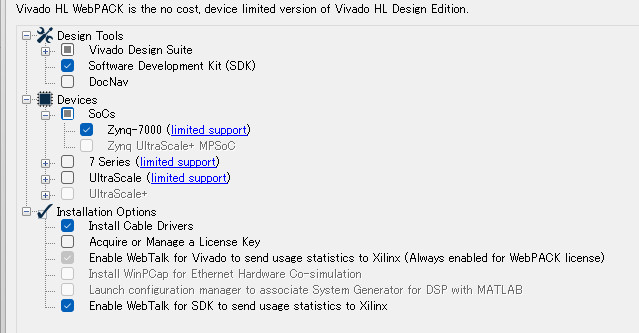

サンプルプロジェクトはVivado 2016.4で作成されているため、AMDのサイトからVivado2016.4をダウンロードしてインストールします。 サンプルプロジェクトを動作させるには、SDKのインストールも必要です。

Board Filesの追加

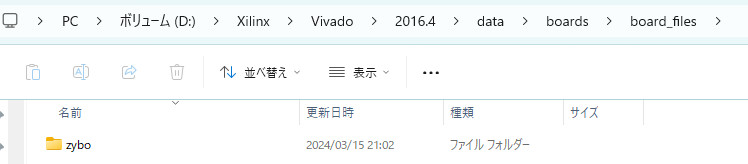

Vivado Board Files for Digilent FPGA Boardsをダウンロードしてzybo用のファイルをVivadoの所定のディレクトリに格納します。具体的には、VivadoのインストールディレクトリがD:\Xilinx\Vivado\2016.4の場合、ダウンロードしたBoard Filesのvivado-boards-master\new\board_files\zyboをD:\Xilinx\Vivado\2016.4\data\boards\board_filesにコピーします。

サンプルデータの展開

Zybo HDMI Output DemoのページにあるリンクからZybo-hdmi-out-2016.4-3.zipをダウンロードして適当なディレクトリに展開します。今回は、D:\work\zybo\Zybo-hdmi-out-2016.4-3\Zybo-hdmi-outに展開しています。

Vivado 2016の起動

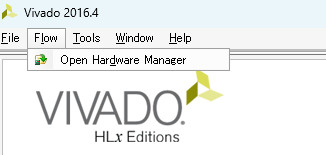

Vivado 2016を起動して、メニューのFlowからOpen Hardware Managerを選択します。

Tcl Consoleでバッチファイルを実行

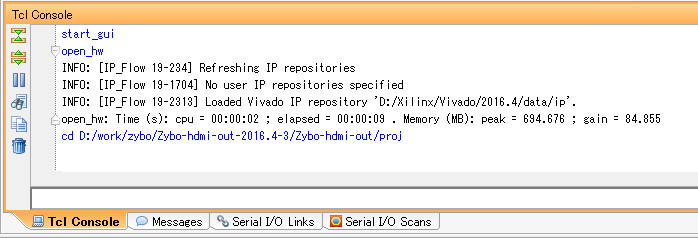

Tcl Consleのコマンド入力でカレントディレクトリをサンプルプロジェクトのprojディレクトリに移動します。Windowsの場合、パスのバックスラッシュ”\”はスラッシュ”/”に変えて入力します。

Tcl Consoleでsource ./create_project.tclを実行します。

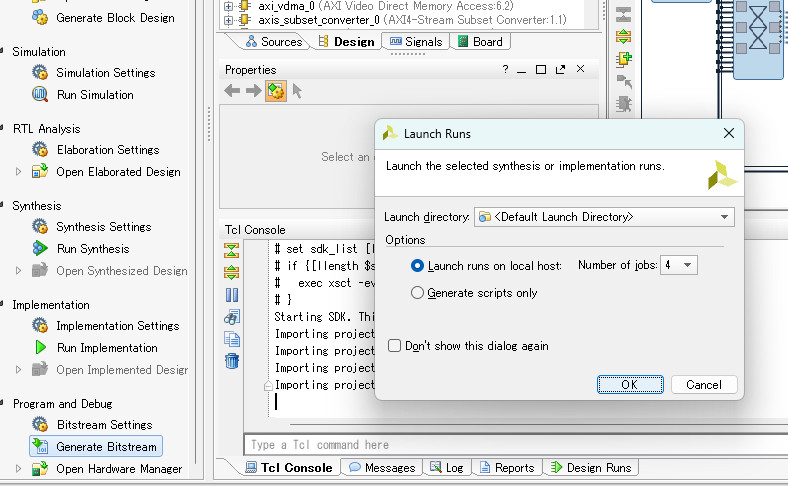

bitstreamの生成

生成されたプロジェクトでGenerate Bitstreamを実行してbitstreamを生成します。

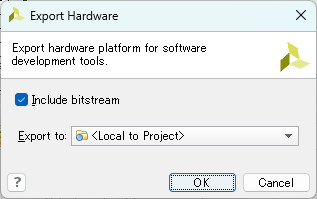

bitstreamが生成できたら、メニューのFile→Export→Export Hardware…を選択して実行します。

SDKでプログラムを生成

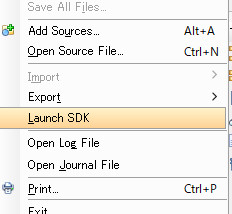

VivadoのメニューからFile→Launch SDKを選択します。

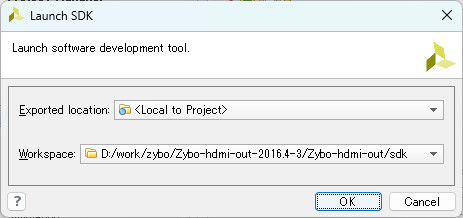

Workspaceにサンプルプロジェクトのsdkを指定してOKをクリックすると、Xilinx SDKが起動します。

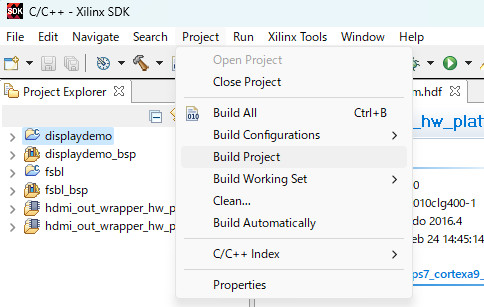

Xilinx SDKの Project Explorerに表示されたdisplaydemoを選択してメニューのProject→Build Projectを実行します。

機器のセットアップ

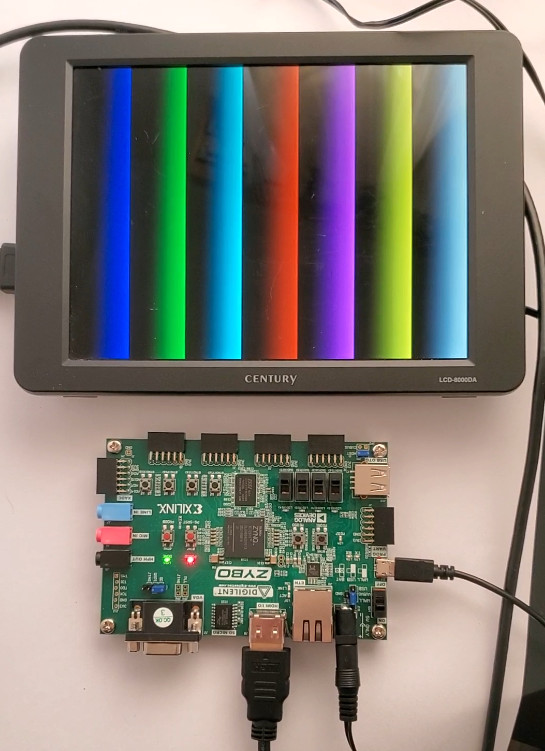

ZyboにHDMIディスプレイを接続して電源を投入します。また、UART用のUSBケーブルでPCと接続します。

プログラムの実行

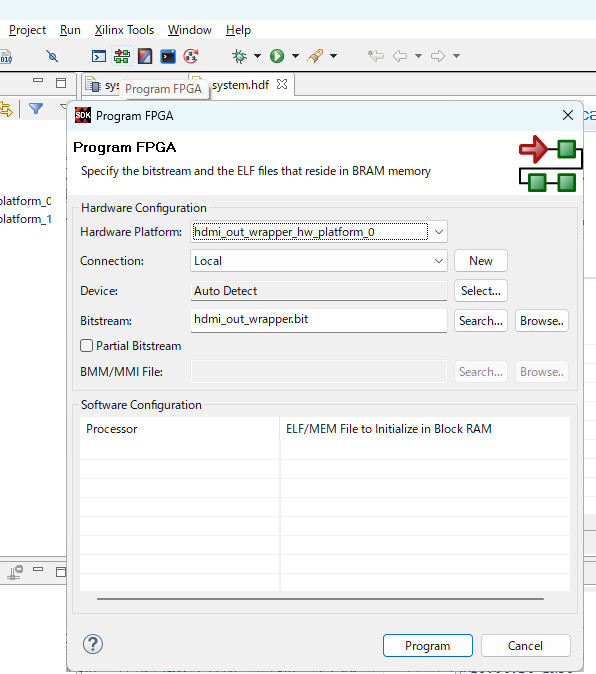

Xilinx SDKのProgram FPGAをクリックして表示されるウィンドウでProgramをクリックしてbitstreamをボードにプログラムします。

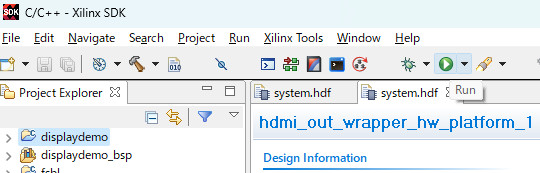

SDKのRunをクリックすると、ディスプレイにカラー画像が表示されます。

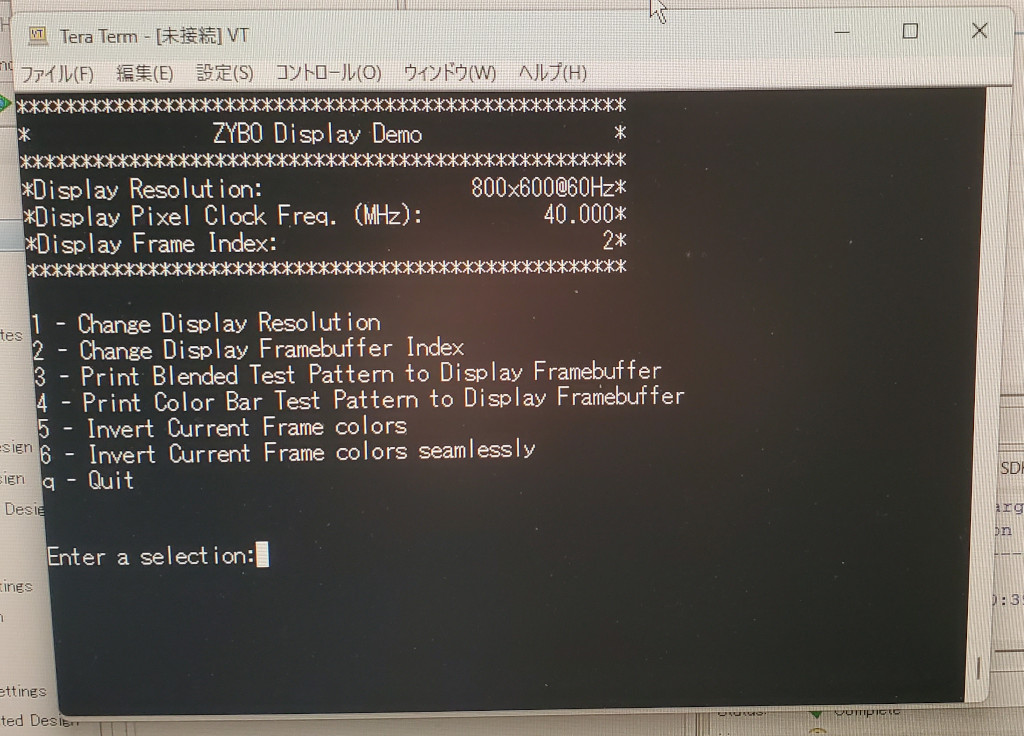

PC上のターミナルから画面の表示を変更することができます。