Vivadoでロジックアナライザを利用する場合、観測したい信号がHDL中に記載されている場合は(* mark_debug = “true” *)の追加が必要でした(Verilogの場合)。Block Design内の信号を観測する場合には、GUIで簡単に指定できます。AXIなど、多数の信号で構成されるバスを、一括して観測対象の信号として指定できるので便利です。具体的な手順は次のとおりです。

1. Block Designを開く

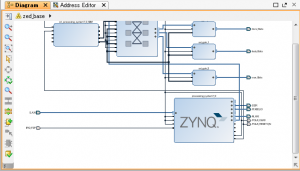

Vivadoで既存のプロジェクトからBlock Designを開きます。

Block Designをオープン

このプロジェクトはZynq-7020のデザインなので、Processing Systemのインスタンスがあります。

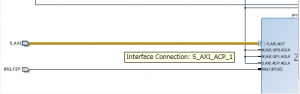

2. 観測する信号の指定

観測したい信号(バス)をマウスで選択します。この例では、Processing Systemから出力されているS_AXI_ACPを選択しています。

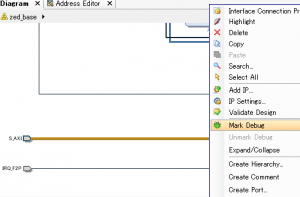

次に、マウスの右クリックからMark Debugを選択します。

Mark Debugを行うと、その信号に緑色のマークが付きます。

また、Tcl Consoleには次の様に表示されます。

set_property HDL_ATTRIBUTE.MARK_DEBUG true [get_bd_intf_nets {S_AXI_ACP_1 }]

true

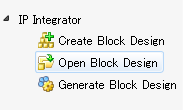

これで観測を行う信号の指定は終了です。個人的にはこの後にTools->Validate Designでデザインを確認、Generate Block Designでデータのアップデート、という処理を行っていますが、もしかするとこの工程は不要かも知れません。

3. Synthesis,implementation,波形表示

Block DesignでMark Debugを行った後の手順は、HDLの場合と同じです。

実際に波形を確認すると、Block DesignでMark Debugを行ったS_AXI_ACPが、ロジックアナライザのDebug Probesでは個々のAXI信号に展開されているのがわかります。

この波形表示はVivado 2015.4で行ったものですが、以前と少しユーザー・インターフェースが変わったようですね。