開発キット

開発キット DE0-Nano-SoCの開封

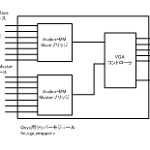

DE0-Nano-SoCはTerasic社製のFPGA開発キットです。Altera社のCyclone V(SE 5CSEMA4U23C6N)が搭載されています。開発キット本体本体は横10cm、縦7cm位の大きさです。表面の中心にCyclon...

開発キット

開発キット  FPGA

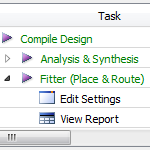

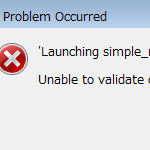

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  設計

設計  設計

設計