計測の目的

ModelSim-Altera Starter Edition(以下ModelSim-ASE)は、デザインがある規模を超えるとシミュレーション速度が低下します(ビジネスモデル的に)。その場合、シミュレーション開始時に次のようなワーニングが表示されます。

# ** Warning: Design size of 150 instances exceeds ModelSim ALTERA recommended capacity. # This may because you are loading cell libraries which are not recommended with # the ModelSim Altera version. Expect performance to be adversely affected.

では実際にどのくらい遅くなるのかということを、GPL Cverとの比較で計測してみました。

計測を行ったシステム

| OS | ubuntu 14.04LTE 64bit |

| プロセッサ | Intel Core i5 |

| メモリ | 8GB |

計測対象のテストベンチと計測方法

2種類のテストベンチ(テスト1とテスト2)について、シミューション時間を計測しました。

テスト1は比較的大規模のデザインで、ModelSim-ASEの推奨デザイン規模を超えているもの、テスト2は推奨デザイン規模を超えていないものです。

シミューション時間の計測は、/usr/bin/timeで行いました。(ModelSim-ASEはvsimの実行時間のみを計測。)

テスト1のテストベンチ詳細

| デザインの概要 | リアルタイム3Dレンダリングシステム |

| シミュレーションの内容 | 小さなグーロシェーディングの三角形2つをレンダリング |

| 推奨デザイン規模 | 超えている |

| その他 | テストベンチでの浮動小数点入力にPLIを利用している |

テスト2のテストベンチ詳細

| デザインの概要 | リアルタイム3Dレンダリングシステム |

| シミュレーションの内容 | 立方体のワイヤーフレームレンダリング |

| 推奨デザイン規模 | 超えていない |

| その他 | テストベンチでの浮動小数点入力にPLIを利用している |

結果

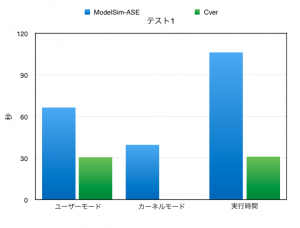

テスト1

ModelSim-ASEのusr/bin/time結果 66.54user 39.76system 1:46.42elapsed 99%CPU (0avgtext+0avgdata 61712maxresident)k 0inputs+5616outputs (0major+10381minor)pagefaults 0swaps GPL Cverのusr/bin/time結果 30.85user 0.14system 0:31.17elapsed 99%CPU (0avgtext+0avgdata 42432maxresident)k 3544inputs+5464outputs (13major+4829minor)pagefaults 0swaps

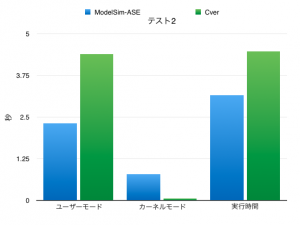

テスト2

ModelSim-ASEの/usr/bin/time結果 2.31user 0.78system 0:03.16elapsed 98%CPU (0avgtext+0avgdata 53360maxresident)k 456inputs+5424outputs (0major+9856minor)pagefaults 0swaps GPL Cverの/usr/bin/timeの結果 4.38user 0.05system 0:04.47elapsed 99%CPU (0avgtext+0avgdata 167028maxresident)k 32inputs+5432outputs (0major+34181minor)pagefaults 0swaps

まとめ

シミュレーション時間は、

- 推奨デザイン規模を超えている時(テスト1)は、GPL Cverの方がModelSim-ASEより約2倍速い

- 推奨デザイン規模を超えていない時(テスト2)は、ModelSim-ASEの方がGPL Cverより約1.5倍速い

という結果になりました。

今回の計測は、「超えた場合」と「超えない場合」でデザインやテストベンチがかなり異なるので、結果は一つの目安程度です。

本当は、推奨デザイン規模ぎりぎりのところを狙ったデザインとテストベンチを使って計測するのがわかりやすいと思いますが、そこまでは行えませんでした。