FPGA

FPGA Cyclone VでACPのアドレス設定を誤った場合の描画結果

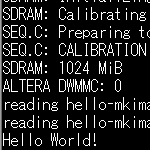

Opencores.orgで公開した3DCG IPコアをDE0-Nano-SoCに移植したところ、描画結果が正しく表示されないという現象が発生しました。ZedBoard版は問題になく表示されているので、AXIなどの基本的な設計部分に問題はな...

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  開発キット

開発キット