DE0-Nano-SoCに搭載されているCyclone Vで、ユーザー回路からHPSにインタラプト信号を接続する手順です。Quartus IIではQsysでHPSの設定などを行いますが、

- インタラプト信号はどうやってQsysに入力すれば良いのか

- HPSのどこに接続すれば良いのか

- インタラプト・ハンドラはどうすれば良いのか

という部分で少し悩みました。今回は、次のような方法でインタラプトを接続しました。

- Qsysで1ビットのPIO(入力)モジュールをインスタンス化する。ユーザー回路からのインタラプトはそこに入力する

- PIOからのインタラプト出力をQsysでHPSのIRQ入力に接続する。

インタラプト信号をQsysに入力する方法はこれ以外にもあるかも知れません。今回の具体的な手順は次の通りです。

Qsysの設定

PIOのインスタンス

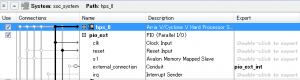

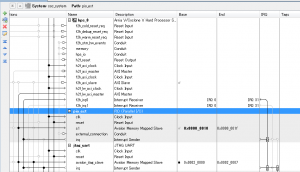

インタラプトを接続するためのPIOをインスタンス化します。この例ではpio_extという名前でインスタンス化しています。external_connectionのExport部分をダブル・クリックするとPIOの入力信号が外部端子になります。名前はpio_ext_intとしました。

次にpio_extをダブル・クリックして詳細を設定します。具体的には、次のように設定します。

- ビット幅1

- 入力方向

- Output Registerなし

- Edge captureなし

- Interruptを生成、タイプはLEVEL

PIOモジュールは、レジスタの初期設定を行う必要があります。このため、s1をHPSのAXIマスタに接続します。今回は、Lightweight AXI Master (h2f_lw_axi_master)に接続しました。アドレス領域は0x0000_0010 – 0x0000_001fとしました。

インタラプト信号について

「Cyclone V Hard Processor System Technical Reference Manual」によると、HPSへのユーザー回路からのインタラプト入力は32本x2 = 64本が用意されています。

FPGA-to-HPS Interrupts

You can configure the HPS component to provide 64 general purpose FPGA-to-HPS interrupts, allowing soft IP in the FPGA fabric to trigger interrupts to the MPU’s generic interrupt controller (GIC). The interrupts are implemented through the following 32-bit interfaces:

• f2h_irq0—FPGA-to-HPS interrupts 0 through 31

• f2h_irq1—FPGA-to-HPS interrupts 32 through 63

The FPGA-to-HPS interrupts are asynchronous on the FPGA interface. Inside the HPS, the interrupts are synchronized to the MPU’s internal peripheral clock (periphclk)

Cyclone V Hard Processor System Technical Reference Manual 28-8 HPS Component Interfaces

Qsysでのインタラプト信号の接続

pio_extのirq出力を、HPSのf2h_irq0またはf2h_irq1に接続します。この例ではf2h_irq0に接続しています。マニュアルに記載されている通り、f2h_irq0とf2h_irq1はそれぞれ32本(32ビット)です。今回のpio_extのインタラプトは1ビットなので、どのビットに割り当てるかを指定する必要があります。この設定はIRQの列に表示されている番号で行います。今回は”0″を設定しています。つまり、pio_extのインタラプトをf2h_irq0[0]に接続しています。

トップモジュールでの信号接続

QsysでHDLを生成後、手作業でユーザー回路からのインタラプト信号を接続します。この例ではw_intがインタラプト信号です。

module ghrd( (省略) ); wire w_int; soc_system u0 ( .pio_led_external_connection_export (LED), //Clock&Reset (省略) : .pio_ext_int_export(w_int) // HPSへのインタラプト入力 ); pp_top u_pp_top ( // system .clk_core(FPGA_CLK1_50), .rst_x(w_pll_locked), .o_int(w_int), //ユーザー回路からのインタラプト出力 (省略)

インタラプト・ハンドラについて

今回、ユーザー回路からのインタラプト信号をf2h_irq0[0]に接続しました。では、これは何を意味するのかというと、GIC(General Interrupt Controller)のInterreupt Number 72に対応するようです。つまり、Interrupt Number 72に反応するようにインタラプト・ハンドラを書けば、ユーザー回路からのインタラプトが認識できるということです。Cyclone V Hard Processor System Technical Reference Manualの”9-14 GIC Interrupt Map for the Cyclone V SoC HPS”という表にはFPGA_IRQ0 – FPGA-IRQ63が定義されていますが、これがf2h_irq0[31:0]とf2h_irq1[31:0]にそのまま対応しているようです。この表ではFPGA_IRQ0がGIC Interrupt Number 72、それから順にFPGA_IRQ63がGIC Intrrupt Number 135という対応が記載されています。