FPGA

FPGA Xilinx SDK 2016.1のコンパイルエラー

OpenCoresで公開したワイヤーフレーム3D CG IPコア(wf3d)は、ZedBoardまたはDE0でサンプル実装を行っています。このサンプル環境には、Vivado 2015.4のXilinx SDKで作成したサンプルアプリが含まれ...

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

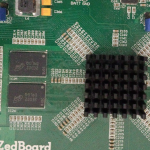

FPGA  開発キット

開発キット  開発キット

開発キット  開発キット

開発キット