Vivado HLSで作成したIPコアで気になるのは、次の点です。

- 本当にHLSで指定した動作周波数で配置配線ができるのか?(本当にタイミング収束するのか?)

なぜこのような点が気になるかというと、従来のASICやFPGAの論理合成ツールでは、実際の配置配線でタイミングが収束しないことが多かったからです(論理合成の時点では配線遅延が確定していないため仕方ありませんが)。Vivado HLSの場合はどうでしょうか。Vivadoに組み込んで確認しました。

Vivado HLSで作成したIP

実験用に作成したのは、簡単な32ビット浮動小数点の乗算器です。ターゲット周波数は200MHzとしました。

- インターフェース:AXI4-Lite

- ターゲット周波数:200MHz

- デバイス:xc7z020clg484-1

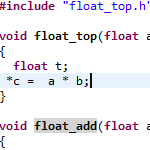

Cコードは次のとおりです。

void float_top(float a, float b, float *c)

{

*c = a * b;

}

また、Directiveは次のとおりです。Interfaceにs_axiliteを指定しています。

set_directive_interface -mode s_axilite "float_top" a set_directive_interface -mode s_axilite "float_top" b set_directive_interface -mode s_axilite "float_top" c set_directive_interface -mode s_axilite "float_top" set_directive_pipeline "float_top"

高位合成の結果は、200MHz(5ns)の要求を満たしています。

| Clock | Target | Estimated | Uncertainty |

| ap_clk | 5.00 | 4.35 | 0.63 |

Vivadoへの組込み

Vivado HLSのExport RTLでIP Catalog用のデータを生成し、Vivadoに組み込みます。ターゲットボードはZedBoardを使用しました。

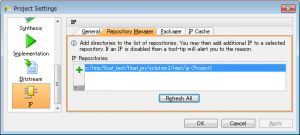

IP Catalogの設定

Vivadoで新しいProjectを作成し、Create Block Designで新しいDesignを作成します。次に、DiagramのIP SettingsアイコンをクリックしてProject Settingsウィンドウを開き、Repository ManagerにVivado HLSで生成したIPのパスを追加します。

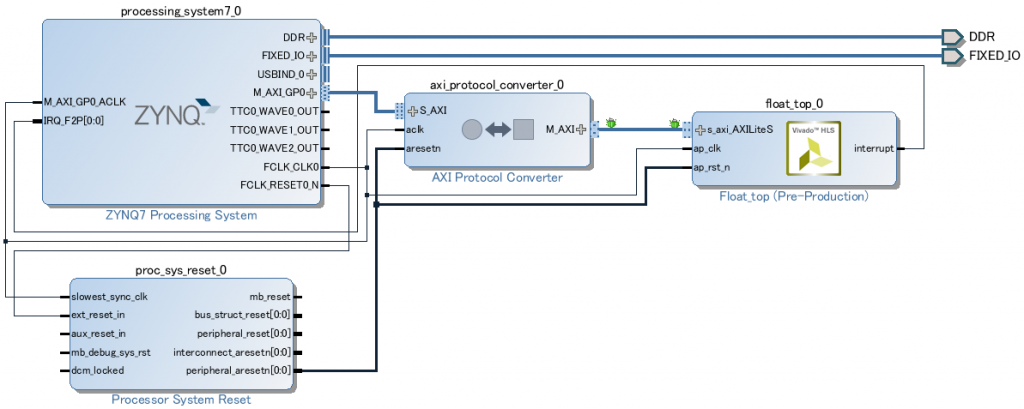

システムの作成

Block Designでprocessing_system7をインスタンス化し、M_AXI_GP0にVivado HLSで生成したIPコアfloat_topを接続します。この時、M_AXI_GP0のプロトコルはAXI3なので、float_topのAXI4-Liteとは直接接続することができません。このため、中間にaxi_protocol_converterを挿入します。

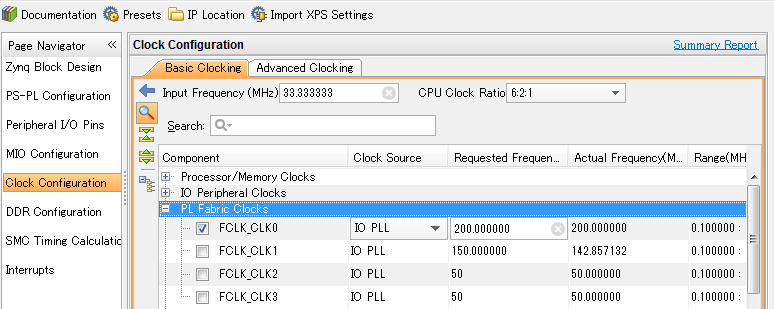

クロックの設定

AXIのクロックは、processing_system7のFCLK_CLK0出力を使用しました。周波数は、Vivado HLSの設定に合わせて200MHzとしました。

合成と配置配線

通常の開発フローに従って、SynthesisとImplementationを実行します。

結果

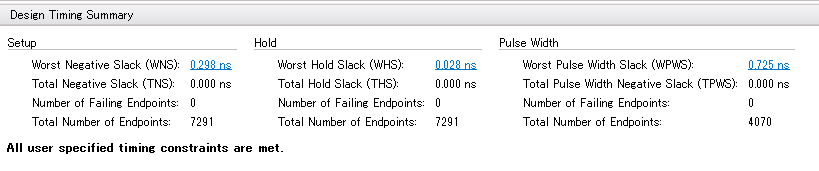

Implementationのレポートを確認すると、問題なく200MHzで配置配線を完了しました。SetupのWNSは0.298nsでした。

まとめ

Vivado HLSで指定したクロック周期は、実際にVivadoの配置配線でタイミング違反無しで収束しました(今回のデザインが非常に簡単なものだったからというのも関係しているかも知れませんが)。