開発キット

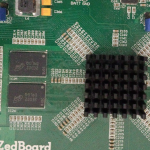

開発キット Spartan-3とZynq-7000を搭載したボードの消費電力比較

元々Spartan-3で実装していたシステムをZynq-7000のシステムに移植しました。消費電力が気になったので、2つのシステムの比較を行いました。アプリケーションは、リアルタイム3Dグラフィクス・アクセラレータです。システムSparta...

開発キット

開発キット  FPGA

FPGA  FPGA

FPGA  開発キット

開発キット  FPGA

FPGA  FPGA

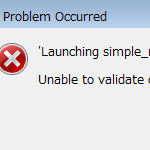

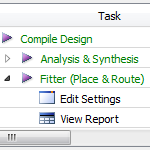

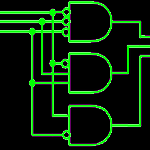

FPGA  設計

設計  jp

jp  jp

jp  jp

jp