設計

設計 yosysで論理合成(フリップ・フロップ)

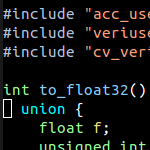

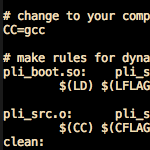

前回はyosysをubuntunにインストールして簡単な基本ゲートの論理合成を行いました。今回は、クロックを使用した設計データの論理合成を試してみます。合成を行う設計データクロックを使用した設計で一番簡単なDフロップ・プロップで論理合成を試...

設計

設計  設計

設計  設計

設計  設計

設計  設計

設計  設計

設計  設計

設計  設計

設計  設計

設計  設計

設計