前回はyosysをubuntunにインストールして簡単な基本ゲートの論理合成を行いました。今回は、クロックを使用した設計データの論理合成を試してみます。

合成を行う設計データ

クロックを使用した設計で一番簡単なDフロップ・プロップで論理合成を試します。具体的なコードは次のとおりです。ファイル名はtest.vです。

module dff ( input i_d, output reg o_d, input rst_x, input clk ); always @(posedge clk or negedge rst_x) begin if (~rst_x) o_d <= 1'b0; else o_d <= i_d; end endmodule

論理合成

合成スクリプト

yosysの合成スクリプトは次のとおりです。セル・ライブラリはyosys付属のcmos_cells.libを利用しています。ファイル名はtest.ysとしました。一般的な論理合成ツールではクロックの設定が必要なのですが、yosysのマニュアルにはそのような記述は見当たりません。例えば、

- クロック名の指定

- クロック周波数の指定

- クロックのデューティ指定

といった設定についての記述は見当たりません。

read_verilog test.v hierarchy proc; opt techmap; opt abc -liberty cmos_cells.lib write_verilog synth.v show clean

論理合成の実行

次のコマンドで論理合成を実行します。

$yosys test.ys

論理結果

合成結果(synth.v)は次のとおりです。Verilogのregがそのまま残っていて、フリップ・フロップのセルに置き換わっていないのがわかります。

(* src = "test.v:1" *)

module dff(i_d, o_d, rst_x, clk);

(* src = "test.v:5" *)

input clk;

(* src = "test.v:2" *)

input i_d;

(* src = "test.v:3" *)

output o_d;

reg o_d;

(* src = "test.v:4" *)

input rst_x;

always @(posedge clk or negedge rst_x)

if (!rst_x)

o_d <= 0;

else

o_d <= i_d;

endmodule

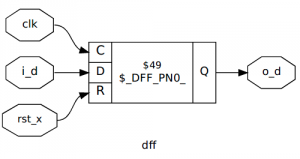

showコマンドで表示される図は次のとおりです。

合成スクリプトの修正

Verilogのregをセルにマッピングするには、合成スクリプトにdfflibmap -libertyを追加します。

read_verilog test.v

hierarchy

proc; opt

techmap; opt

dfflibmap -liberty cmos_cells.lib

abc -liberty cmos_cells.lib

write_verilog synth.v

show

clean

再合成結果

dfflibmapを追加した合成スクリプトを実行すると、regがセルにマッピングされた次のネットリストが生成されます。

(* src = "test.v:1" *)

module dff(i_d, o_d, rst_x, clk);

wire _0_;

wire _1_;

wire _2_;

(* src = "test.v:5" *)

input clk;

(* src = "test.v:2" *)

input i_d;

(* src = "test.v:3" *)

output o_d;

(* src = "test.v:4" *)

input rst_x;

NOT _3_ (

.A(_0_),

.Y(_1_)

);

DFFSR _4_ (

.C(clk),

.D(i_d),

.Q(o_d),

.R(_2_),

.S(1'b0)

);

assign _0_ = rst_x;

assign _2_ = _1_;

endmodule

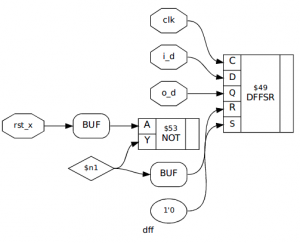

showの結果は次のとおりです。Verilogソース・コード中のo_dというregがDFFSRというフリップ・プロップにマッピングされていることがわかります。

まとめ

yosysを使ってクロック入力のある簡単な設計データの論理合成を行いました。一般的な論理合成ツールでは、クロックに対して周波数などの設定が必要になりますが、yosysには存在しないようです(少なくとも今のバージョンでは)。