インターネット・プロトコル・スイート

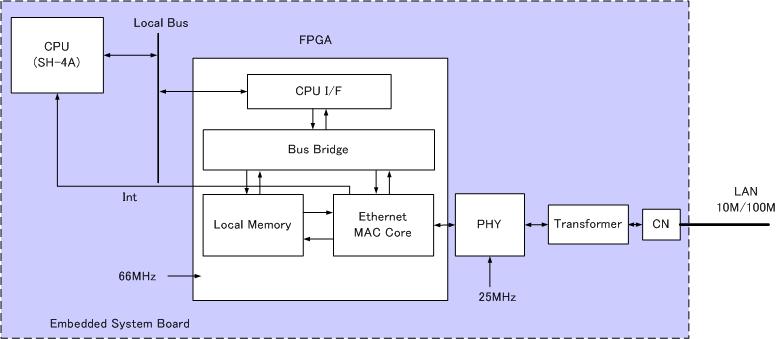

リンク層のハードウェア部分は、CPUとEthernet MAC Coreを格納するFPGAを中心としたシステムで実現しています。

ハードウェアシステム構成

システムの概要は次の通りです。

システム構成図

- CPUはSH-4A

- Ethernet MAC Coreは、Local Busに接続されたFPGA(Spartan3 XC3S400)に格納

- Ethernet MAC Coreが使用するバッファにはFPGA内部RAM(Block RAM)を使用

- 外付けPHY(LAN83C185)はMIIでFPGAと接続

- PHYはパルス・トランス(TLA-6T118)を経由してRJ45コネクタに接続

- FPGA基本クロックは66MHz(Local Busクロック)

- PHYには25MHzのクロックを供給

- 送受信完了などの通知用として、CPUへのインタラプト信号を1本使用(IRQ2)

FPGA内部構成

FPGA内部は、Ethernet Coreを含めて、次の4つのモジュールで構成されます。

| Module名 | 説明 |

|---|---|

| CPU I/F | CPU(SH-4A)バスインターフェース |

| Bus Bridge | CPUバスとWHISHBONE*1のブリッジ回路 |

| Ethernet MAC Core | CpenCores Ethernet IP core |

| Local Memory | 送受信Frame格納用バッファ |

CPU I/Fは、SH-4AのLocal Busのインターフェース回路です。Local BusはSRAMインターフェースに設定されており、SH-4A CS2空間のシングルRead/Write転送を受け付けます。Bus Bridgeは、WISHBONEとのインターフェースを変換するブリッジ回路です。Local MemoryはFPGAのBlock RAMで構成された4K ByteのSRAMメモリであり、Ethernet MAC Coreの送受信Frameデータを格納します。Ethernet MAC Coreは、DMAマスタとなってLocal Memoryに格納された送信Frameデータを読み出し、PHYに対して出力します。また、PHYから受信Frameデータが入力された時には、をLocal Memoryに格納します。

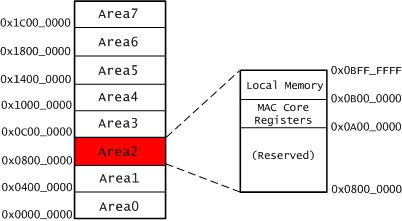

メモリマップ

FPGAの内部リソースは、SH4のエリア2にマッピングされています。Ethernet MAC Coreのレジスタは0x0A00_0000-0x0A00_07FF、4K ByteのLocal Memoryは、0x0A80_0000-0x0A80_0FFFにそれぞれマッピングされています。

SH4メモリマップ

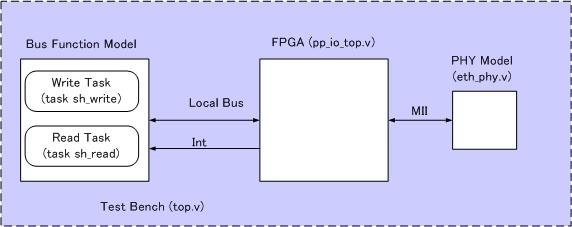

RTLシミュレーション

基本的な機能の動作確認は、RTLシミュレーションで行います。シミュレーションでは、実機でCPUが行う処理部分をバスファンクションモデルで単純化しています。また、PHY部分には、Ethernet IP Coreに含まれているPHYビヘイビアモデルをMIIで接続して使用しています。

テストベンチの構成

シミュレーションは、機能ごとに定義されたtaskを順次呼び出しながら実行されます。次のテストベンチでは、PHYとEthernet MAC Coreの初期レジスタ設定後、Ethernet Frameの送信と受信を行っています。

(テストベンチtop.v抜粋)

/***********************************************

Main test routine

***********************************************/

initial begin

reset;

phy_setup;

register_setup;

set_tx_frame;

send_tx_frame;

set_rx_frame;

receive_rx_frame;

repeat (1000) @(posedge L_CLK); // inter packet gap

receive_rx_frame;

repeat (100) @(posedge L_CLK);

$finish;

end

論理合成

ISEを用いた論理合成の結果、FPGA使用リソースは以下の様になりました。

| Logic Utilization | |

| Number of Slice Flip Flops | 1,232 out of 7,168 17% |

| Number of 4 input LUTs | 2,417 out of 7,168 33% |

| Logic Distribution | |

| Number of occupied Slices | 1,618 out of 3,584 45% |

| Number of RAMB16s | 6 out of 16 37% |

*1 OpenCoresで推奨されているSoC用インターコネクト規格