FPGA

FPGA Vivado HLSメモ

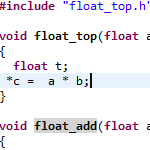

Vivado HL WebPACK EditionからVivao HLS(高位合成)を無償で試せるようになりました。Vivado HLSを使うと、CやC++で記述したコードからVerilogやVHDLのコードが生成できます。Vivado 2...

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA