FPGA

FPGA ISEのxstをコマンドラインから実行する

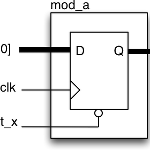

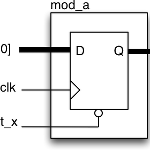

xstはISE標準の論理合成ツールです。論理合成可能なVerilogやVHDLのコードをネットリストに変換します。VerilogのサポートはVerilog2001です。SystemVerilogはサポートされていません。xstをコマンドライ...

FPGA

FPGA  FPGA

FPGA  開発キット

開発キット  開発キット

開発キット  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  設計

設計  設計

設計