設計

設計 Icarus Verilogのインストール

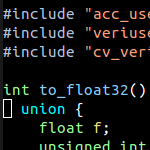

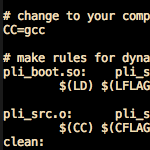

Mac OS X YosemiteにIcarus Verilogをインストールしました。Icarus Verilogはオープンソース(GNU General Public License)のVerilogシミュレータです。インストール手順は...

設計

設計  設計

設計  設計

設計  OpenCores

OpenCores  OpenCores

OpenCores  OpenCores

OpenCores  設計

設計  設計

設計  設計

設計  設計

設計