Zynq-7000は3種類のAXI(AXI_GP,AXI_HP,AXI_ACP)をサポートしていますが、いずれもAXIのバージョンはAXI3です。AXI4とAXI3にはいくつかの違いがありますが、大きな違いの1つが最大バースト長です。AXI4の最大バースト長は256ですが、AXI3の最大バースト長は16です。このため、AXIに接続しようとしているユーザー回路がAXI4であり、16より長いバーストを必要とする場合にはZynq-7000のAXIにそのままでは接続できません。このような場合、VivadoのIPコアを使うと簡単にAXI4をAXI3に変換できます。

AXI4からAXI3の変換

AXI Protocol Converterのインスタンス化

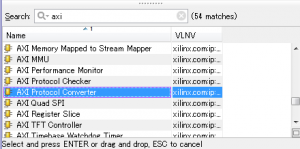

AXI4からAXI3への変換は、IPコアカタログでAXI Protocol Converterを検索し、それをインスタンス化するだけです。

AXI Protocol Converterの接続

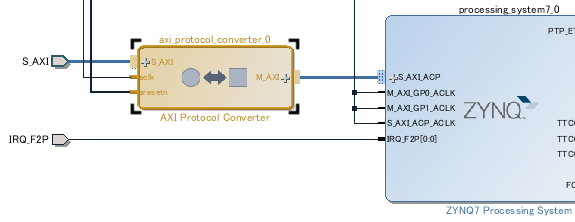

次の例では、AXI Protocol Converterをaxi_protocol_converter_0としてインスタンス化しています。また、ユーザー回路からのAXI4外部入力(S_AXI)を変換してZYNQ7のS_AXI_ACPに接続しています。このような場合、axi_protocol_converter_0のS_AXI側にユーザー回路からS_AXIを接続し、M_AXIにZYNQ7のS_AXI_ACPを接続します。

AXI Protocol Converterのパラメータ設定

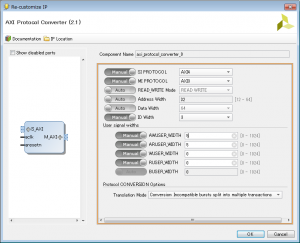

AXI Protocol Converterのインスタンスをダブルクリックすると、パラメータを設定できます。AXI4をAXI3に変換する場合、SI PROTOCOLをAXI4、MI PROTOCOLをAXI3とします。

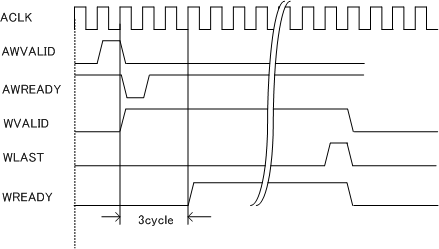

実際の波形

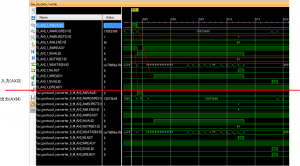

AXI Protocol Converterを挿入すると、ユーザー回路側のAXI応答がS_AXI_ACPと比べて少し変わります。次の波形は、ユーザー回路からS_AXI_ACP経由でメインメモリ(DDR3)にバースト16のライトを行ったものです。AXIの動作周波数は50MHz、DDR3の動作周波数は533MHz(データ転送速度:1066MHz)です。

ロジックアナライザの波形から、ユーザー回路側のAXI応答を抜粋したのが下図です。ZYNQ7のS_AXI_ACPは、基本的にAWREADYとWREADYはデフォルトでHレベルですが、AXI Protocol Converterを挿入すると、次のような応答になるようです。

- AWREADYはデフォルトでHレベルだが、AWVALID受付後は1サイクルだけLレベルになる

- WREADYはデフォルトでLレベルになる。AWVALID受付から3サイクル後に、バースト長分だけHレベルになる

「必ず最初にライトコマンドを受け、次に対応するライトデータを受け付ける」という処理が行われているようです。このようなAXI応答になっても、一般的な設計では特に困ることはないと思いますが、ライトデータを先に出力しなければならない設計の場合には注意が必要かもしれません。