Cyclone Vの内部は、Cortex-A9を内蔵したHPS(Hard Processor System) Portionと、ユーザー回路をプログラムできるFPGA Portionで構成されています。FPGA Portionに実装したユーザー回路がHPS Portionに接続されたDDR3メイン・メモリをアクセスしたい場合、HPS PortionとAXIで接続します。この時、ユーザー回路側がマスタとなるAXIとしては、次の2種類が選択できます。

- FPGA-to-HPS Bridge

- FPGA-to-SDRAM Interface

FPGA-to-HPS Bridgeは、キャッシュ・フラッシュを気にしなくて良いACP(Accelerator Coherency Port)を利用できるのが特徴です。FPGA-to-SDRAM Interfaceは、ACPやペリフェラルのアクセスは行えませんが、その代わりに4GBのメイン・メモリをリニアにアクセスできるのが特徴です。今回、FPGA Portionにユーザー回路を実装してFPGA-to-HPS BridgeのAXIの応答をSignal Tap IIで観測してみました。使用した開発キットはDE0-Nano-SoCです。

FPGA-to-HPS BridgeのAXI応答

AXIの設定など

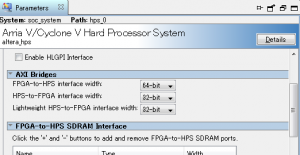

AXIの設定は次の通りです。

| AXIクロック周波数 | 50MHz |

| データ・バス幅 | 64ビット |

| バースト・タイプ | INCR |

| バースト長 | 16 |

| AxCACHEの値 | すべて1 |

FPGA-to-HSP Bridgeとユーザー回路は、ダイレクトに接続しています。途中にプロトコル変換やバス幅変換のモジュールは接続していません。QsysでのHPS設定は次の通りです。

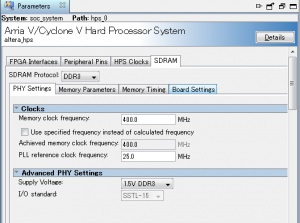

DDR3は標準の設定(DE0-Nano-SoCのサンプルの設定)をそのまま使用しています。

ソフトウェアについて

Linuxとベアメタルの2種類でアプリを実行しました。

観測結果

リードとライトアクセスについて、それぞれバースト長16のアクセスを観測しました。また、アクセス先のアドレスはDDR3メイン・メモリです。アクセスは、すべてACPを有効にしています。つまり、8000_0000hのオフセットをアドレスに加えてDDR3をアクセスしています。

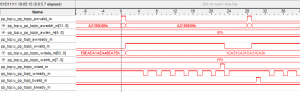

ライト

AXIではライト・コマンドとライト・データの関係は特に決まっていませんが、今回のAXIマスタは、ライト・コマンドが受け付けられた直後のサイクルから、バースト長分のライト・データを連続して出力します。このようなAXIライトを行うと、ライト・コマンドはウェイトなしでAXIに送出されました(AWVALID=HかつAWREADY=H)。ライト・データはウェイト・サイクル(WREADY=L)が観測されました。具体的には、4バースト後に1サイクルのウェイト・サイクルが入り、その後2バーストごとに1サイクルのウェイト・サイクルが入りました。

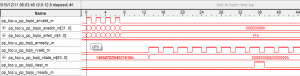

リード

リード・コマンドもウェイト・サイクルなしの1サイクルで受け付けられました(ARVALID=HかつARREADY=H)。この例の場合、1サイクルを空けてリード・コマンドを4回発行しています。バースト長16のリード・データは、連続ではなく分割されて戻ってきました。具体的には、13サイクル後に最初のリード・データが戻り、その後有効データ(RVALID=H)が2サイクル、次に1ウェイト(RVALID=L)が1サイクルという繰り返しで16のデータが戻ります。

まとめ

DDR3の動作周波数が400MHz(データ転送は800MHz)、データ・バス幅が32ビットなので、50MHzに換算すると、1サイクルのデータ・バス幅は512ビットになります(400MHzで64ビット->200MHzで128ビット->100MHzで256ビット->50MHzで512ビット)。今回のユーザー回路のAXI動作周波数は50MHzなので、リード、ライトともに連続してデータを転送するのに十分な余裕がありそうに思いましたが、実際にはウェイト・サイクルが観測されました。パラメータなど、設計で調整が必要な部分があるのかも知れません。

なお、波形は動作中のあるタイミングでのスナップ・ショットなので、すべてのAIX転送がこのような応答をしているとは限りません。ただ、全体的にはこのような傾向が観測されました。

また、Linux上でアプリを動かしても、ベアメタルでアプリを動かしてもAXIの応答に大きな違いはありませんでした。