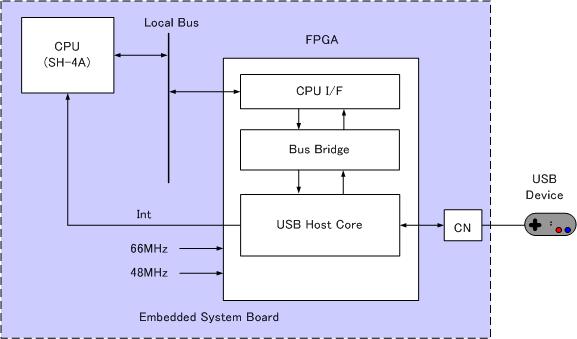

System Architecture

The following shows the building blocks for the FPGA.

System Architecture

- CPU is SH-4A

- All functional blocks including USB HostSlave IP Core are placed in one FPGA(Spartan3 XC3S400) connected to CPU local bus

- USB signals are connected from USB Type-A connector to the FPGA via bus switch IC

- 66MHz for FPGA core clock( CPU local bus clock)

- 48MHz for USB Host Core

- Commercial available game pad is used as a USB device

- An interrupt signal is used for communication between CPU and FPGA(IRQ1)

Modules in FPGA

FPGA top module is constructed with three modules.

| Module Name | Description |

|---|---|

| CPU I/F | CPU(SH-4A) bus interface |

| Bus Bridge | Bridge interface between CPU bus and WHISHBONE*1 |

| USB Host Core | OpenCores USB Host/Slave Core |

CPU I/F module is an interface module for SH-4A Local Bus. Local Bus protocol is configured to SRAM type, mapped on CS2 space, and accept single read/write transfer. Bus Bridge module converts interface protocols between CPU and WISHBONE. USB HostSlave IP Core has 8-bit width register configuration bus. This 8-bit width register space is mapped directly to 32-bit CPU addressing space for simple implementation (without 8-bit to 32-bit addressing conversion) As a result, upper 24bits in CPU data bus is not used.

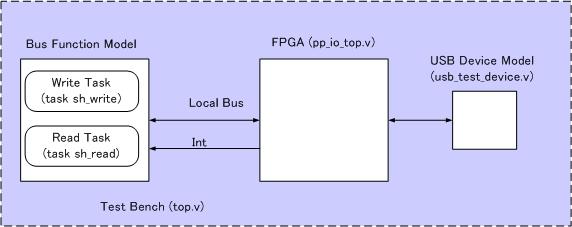

Simulation

Simulation Environment

Functional simulation environment contains FPGA top module, USB device model, and CPU Bus Function Model(BFM). BFM is written in verilog task and handles CPU local bus read/write transaction. USB device model is a test slave device which is included in USB HostSlave IP Core simulation environment. The main test scenario is ported from the original scenario(testCase0.v). The main check point is to confirm CPU Interface and Bus Bridge behavior.

Logic Synthesis

The following shows FPGA resource usage, synthesized with xst in ISE.

| Logic Utilization | |

|---|---|

| Number of Slice Flip Flops | 1,144 out of 7,168 15% |

| Number of 4 input LUTs | 1,871 out of 7,168 26% |

| Logic Distribution | |

| Number of occupied Slices | 1,268 out of 3,584 35% |

| Number of RAMB16s | 4 out of 16 25% |

*1 An interconnect architecture which is recommended in OpenCores project.