OpenCores

OpenCores 挑戦!OpenCoresにIPコアを登録(その1)

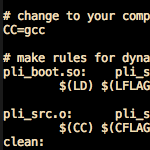

OpenCoresにIPコアを登録するにはどうすればよいでしょうか?OpenCoresのサイトのFAQページが参考になります。このページのTerms and conditionsの"To create project"には次のように書かれて...

OpenCores

OpenCores  OpenCores

OpenCores  設計

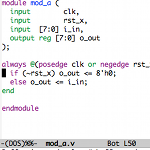

設計  設計

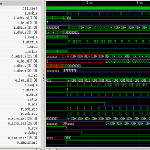

設計  FPGA

FPGA  設計

設計  設計

設計  FPGA

FPGA  設計

設計  設計

設計