Vivado 2015.4が前提のArty Getting Started with Microblazeチュートリアルを、Vivado2020.1で実行したときのメモです。

チュートリアルの冒頭に「このガイドは古いので、こちらを参照してください」というリンクがありますが、リンク先は少し内容が異なります。

Vivado部分

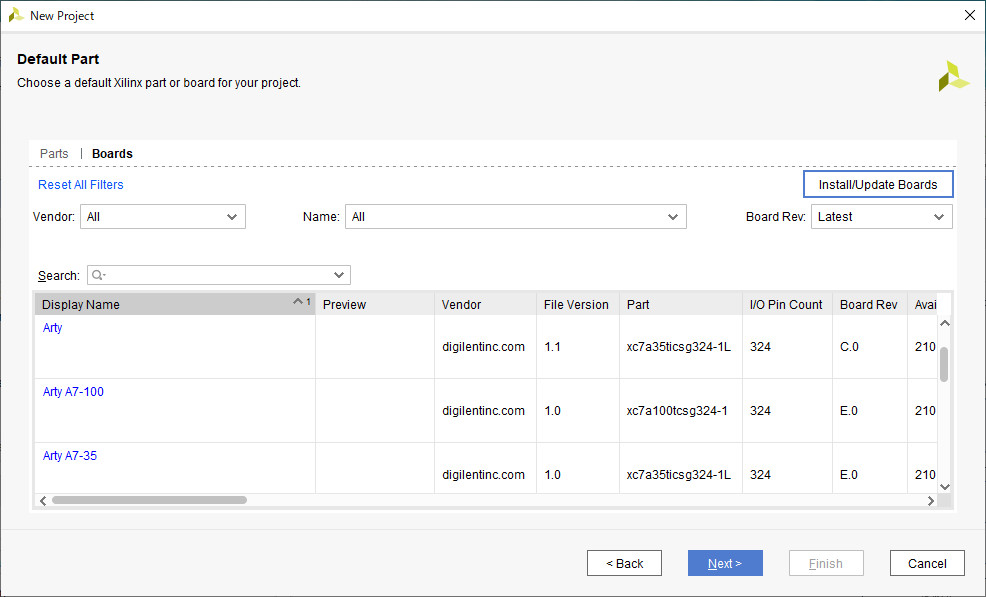

事前に、Arty用のボードサポートファイルをVivadoに追加しておく必要があります。ボードサポートファイルを追加しないと、プロジェクト作成時にArtyが選択肢に表示されません。最近のArtyはFPGAをA7-35TとA7-100Tから選べるようで、ボードサポートファイルも2種類存在します。

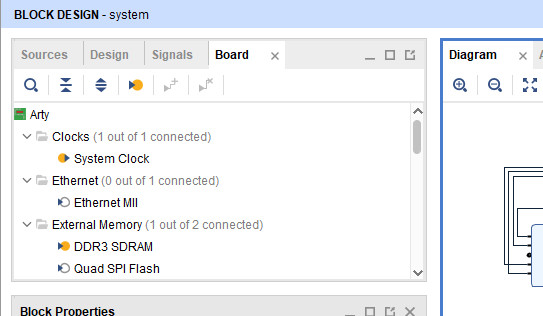

ブロックデザインの作成から、ビットストリームの作成までは、Vivado 2015.4とVivado2020.1で特に違いはありません。ただ、久しぶりにVivadoを使ったので、使用するコンポーネントを間違えてIPカタログから探してしまいました。正しくは左側のBoardタブからコンポーネントを選択します。このチュートリアルでIPカタログを使うのはMicroBlazeだけです。

ビットストリームを生成したら、File->Export->Export Hardwareで以下を設定してXSAファイルを生成します。

- Platform type: Fixed

- Output: Include bitstream

Vitis部分

プロジェクト作成

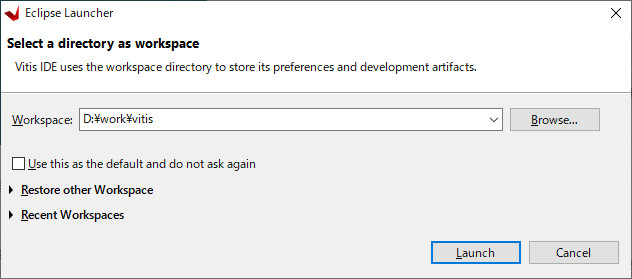

Vivado 2015.4とVivado2020.1は、SDK部分が大きく異なります。Vivado2020.1は、Xilinx SDKの代わりにVitisを使用します。まず、VivadoのTools->Launch Vitis IDEからVitisを起動し、Workspaceを指定してLaunchします。

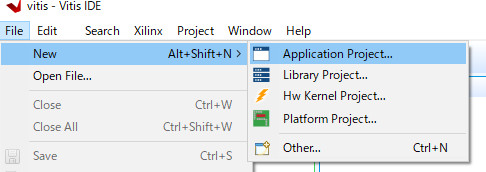

File->New->Application Project…でプロジェクトを作成します。

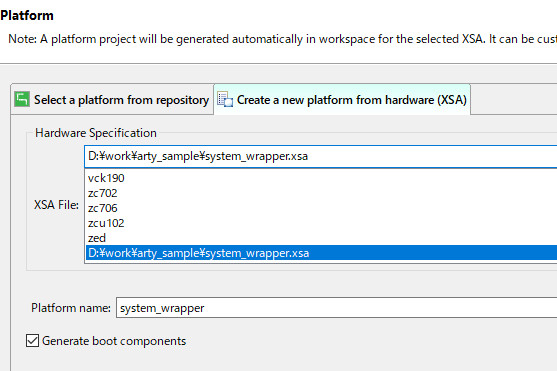

PlatformでCreate a new platform from hardware(XSA)タブを選択して、Browseボタンで生成済みのXSAファイルを指定します。

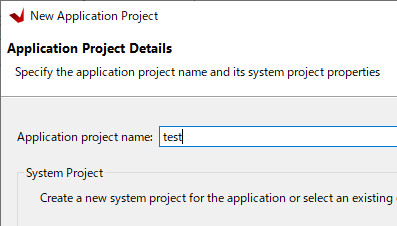

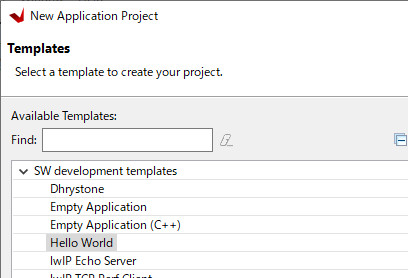

プロジェクト名を指定して、domainはデフォルト、TemplatesはHello Worldを指定してプロジェクトを作成します。

ビットストリームのロード

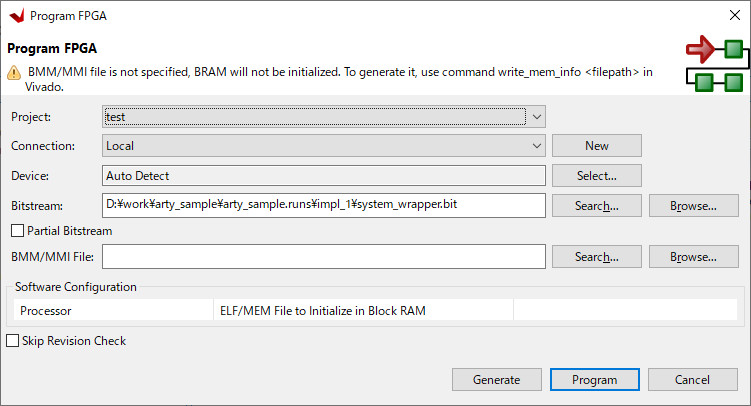

Xilinx->Program FPGAからVivadoで生成したビットストリームをプログラムします。

アプリの実行

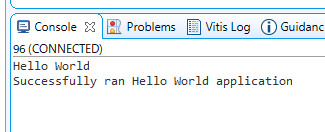

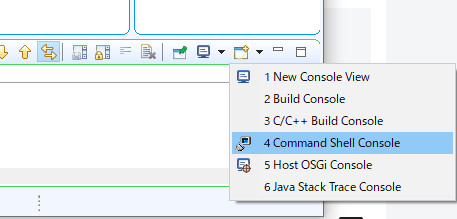

チュートリアルではUARTの出力をTera Termに表示していますが、Vitisだけでも出力を確認できます。Vitisで確認するには、Vitisの下段右側付近のOpenConsoleから4 Command Shell Consoleを選択します。

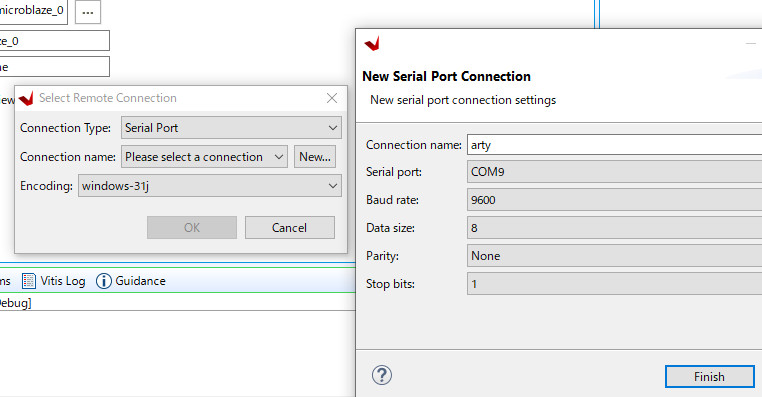

Connection TypeにSerial Portを指定して、Connection nameのNew…で表示されるウィンドウでシリアルポートの設定を行います。Connection nameは適当に指定します。 Baud rateはUSB UARTの設定に合わせます。デフォルトのままであれば、9600です。

OKをクリックすると、シリアルポートに接続されます。

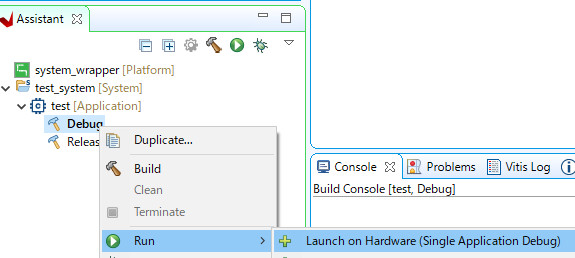

AssistantのDebugを右クリックして表示されるメニューからBuildを実行後、Run->Launch on Hardware(Single Application Debug)を選択すると、コンソールにHello worldが表示されます。