Windows10のTcl Shell上でVivado Simulatorをコマンドライン実行する時の手順です。

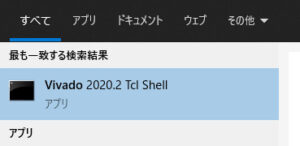

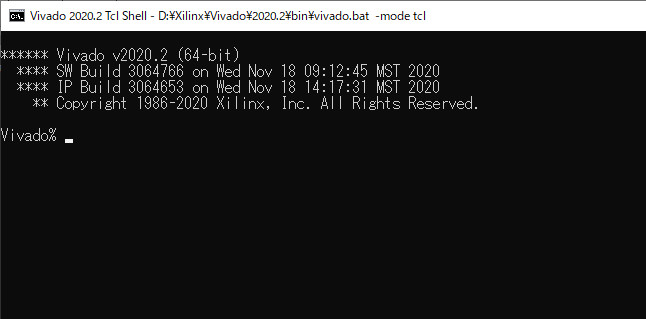

Tcl Shellの起動

WindowsのスタートメニューからVivado Tcl Shellを起動します。

ディレクトリ変更

シミュレーションを実行するディレクトリに移動します。この例では、d:\work\spi\workです。

Vivado%cd d:\work\spi\workシミュレーション実行用tclスクリプト

次のようなtclスクリプト(test.tcl)を作成します。

- テストベンチのファイルは、スクリプト外部からsim_fileに設定します。

- テストベンチのトップモジュールは、TOP_MODULEに設定します。

- シミュレータコマンドとして、xvlog, xelab, xsimを実行します。

- シミュレータコマンドは、execを使って実行します。

- RTLディレクトリは、../rtlです。

- RTLのインクルードディレクトリは../includeです。

# test.tcl

set sim_file [lindex $argv 1]

puts "Test Scenario= $sim_file"

# RTL directory

set RTL_DIR "../rtl"

set INC_DIR "../include"

# Top module

set TOP_MODULE "top"

# compile

set ret [exec xvlog\

-sv\

-i $INC_DIR\

--sourcelibdir $RTL_DIR\

--sourcelibext .v\

$sim_file ]

puts $ret

# elaboration

set ret [exec xelab \

--debug all \

--notimingchecks \

$TOP_MODULE ]

puts $ret

# simulation

set ret [exec xsim $TOP_MODULE\

--runall]

puts $ret

引数の設定

Tcl Shellでtclスクリプトに渡すテストベンチのファイル名を設定します。

- argvがtclスクリプトへの引数に相当します。リストの2番目にファイル名(../scenario/test1.v)を設定しています。

- argcは引数の数です。

Vivado% set argv [list test ../scenario/test1.v]

test ../scenario/test1.v

Vivado% set argc 2

2tclスクリプトの実行

Tcl Shellでtclスクリプトをsourceすると、シミュレーションが実行されます。

Vivado% source ../bin/test.tcl

# set sim_file [lindex $argv 1]

# puts "Test Scenario= $sim_file"

Test Scenario= ../scenario/test1.v

# set RTL_DIR "../rtl"

# set INC_DIR "../include"

# set TOP_MODULE "top"

# set ret [exec xvlog\

# -sv\

# -i $INC_DIR\

# --sourcelibdir $RTL_DIR\

# --sourcelibext .v\

# $sim_file ]

# puts $ret

INFO: [VRFC 10-2263] Analyzing SystemVerilog file "scenario/test1.v" into library work

INFO: [VRFC 10-311] analyzing module top

# set ret [exec xelab \

# --debug all \

# --notimingchecks \

# $TOP_MODULE ]

# puts $ret

Vivado Simulator 2020.2

Copyright 1986-1999, 2001-2020 Xilinx, Inc. All Rights Reserved.

Running: xelab.exe --debug all --notimingchecks top

Multi-threading is on. Using 6 slave threads.

Starting static elaboration

Pass Through NonSizing Optimizer

Completed static elaboration

Starting simulation data flow analysis

Completed simulation data flow analysis

Time Resolution for simulation is 1ns

Compiling module work.top

Built simulation snapshot work.top

# set ret [exec xsim $TOP_MODULE\

# --runall]

# puts $ret

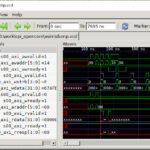

****** xsim v2020.2 (64-bit)

**** SW Build 3064766 on Wed Nov 18 09:12:45 MST 2020

**** IP Build 3064653 on Wed Nov 18 14:17:31 MST 2020

** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved.

source xsim.dir/work.top/xsim_script.tcl

# xsim {work.top} -autoloadwcfg -runall

Vivado Simulator 2020.2

Time resolution is 1 ns

run -all

$finish called at time : 100 ns : File "scenario/test1.v" Line 16

exit

INFO: [Common 17-206] Exiting xsim at Thu Jul 15 xx:xx:xx 2021...

Vivado%