FPGA

FPGA デザインに変更を加えた後にNios II Eclipseで必要な処理

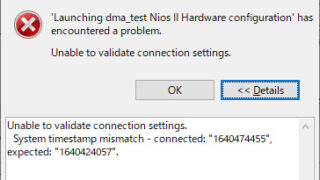

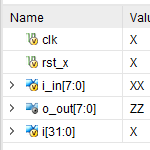

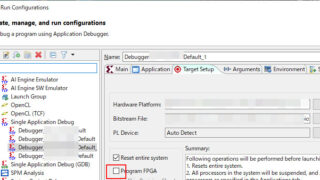

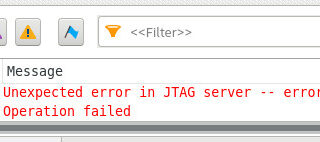

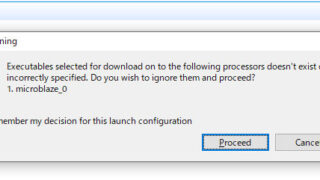

デザインを変更してQuartus Primeでコンパイルを実行した後、Eclipseからプログラムを実行しようとすると、次のようなエラーが発生します。Generate the BSP to update the Makefile, and ...

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

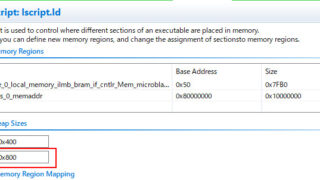

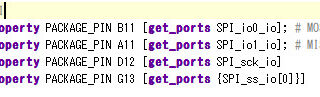

FPGA  設計

設計  設計

設計  設計

設計