設計

設計 VivadoのUART

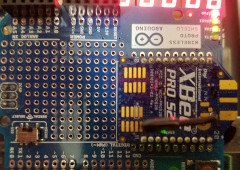

Vivado/Vitis v2020.1でArtyのArduino/chipKIT Shield Connectorからシリアルデータを取り込んだ時のメモです。ArtyのArduino/chipKIT Shield ConnectorViv...

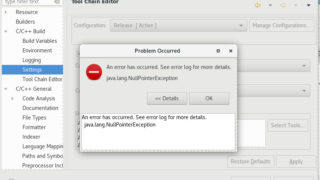

設計

設計  設計

設計  設計

設計  設計

設計  設計

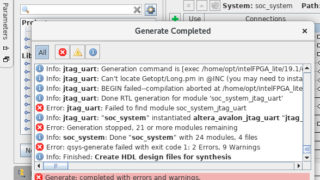

設計  FPGA

FPGA  設計

設計  設計

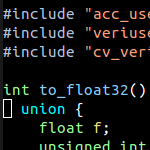

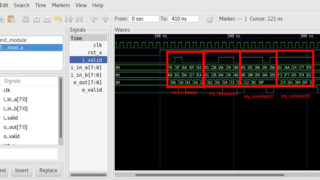

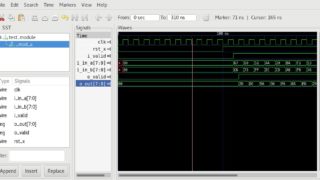

設計  機能検証

機能検証  機能検証

機能検証