FPGA

FPGA DE0-Nano-SoC用ベアメタルアプリとFPGAコンフィギュレーション

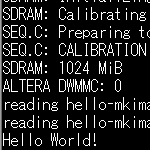

DE0-Nano-SoCのベアメタルアプリをSDカードからブートするとき、FPGAのコンフィギュレーションも同時に行う場合の手順です。ベアメタルアプリとFPGAコンフィギュレーションFPGAのコンフィギュレーションは、HPSでFPGAのデー...

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA