システム構成

今回、実装を行うシステムの構成です。

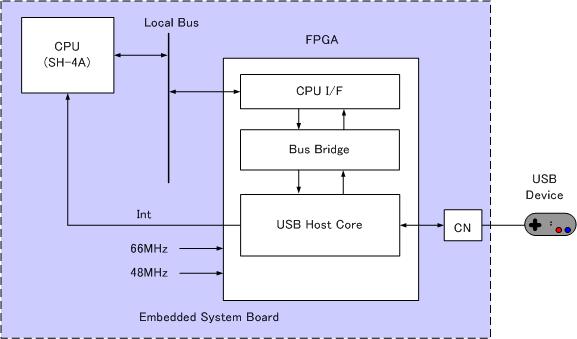

システム構成図

- CPUはSH-4A

- USBホストCoreを含むすべての回路は、Local Busに接続されたFPGA(Spartan3 XC3S400)に格納

- USB TYpe-AコネクタからのUSBバス信号が、バススイッチICを経由してFPGAに接続されている

- FPGA基本クロックは66MHz(Local Busクロック)

- USBホストCore用に48MHzを使用

- USBデバイスとして、特殊なデバイスドライバを必要としないゲームPADを利用

- CPUへのインタラプト信号を1本使用(IRQ1)

FPGA内部構成

USBホストCoreを中心に周辺回路を追加して、FPGA用のトップモジュールを作成します。FPGA内部は、USBホストCoreを含めて3つのモジュールで構成されます。

| Module名 | 説明 |

|---|---|

| CPU I/F | CPU(SH-4A)バスインターフェース |

| Bus Bridge | CPUバスとWHISHBONE*1のブリッジ回路 |

| USBホストCore | CpenCores USB Host/Slave Core |

CPU I/Fは、SH-4AのLocal Busのインターフェース回路です。Local BusはSRAMインターフェースに設定されており、SH-4A CS2空間のシングルRead/Write転送を受け付けます。Bus Bridgeは、WISHBONEとのインターフェースを変換するブリッジ回路です。USBホストCoreは、8ビット幅のレジスタ設定バスで設計されていますが、今回はSH-4Aの32ビットバスにそのまま接続し、上位24ビット部分を未使用としました。

シミュレーション

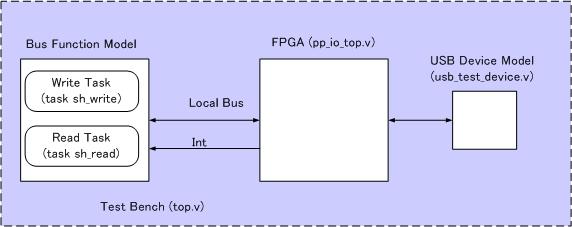

テストベンチの構成

ターゲットシステムでCPUが行う処理部分をバスファンクションモデルに置き換えてシミュレーションを実行します。バスファンクションモデルは、Local BusでのCPUのRead/Write処理を受け持ちます。USBホストCoreのテストベンチtestCase0.vを参考に、CPUからのレジスタ設定でUSBホストCoreの動作を確認します。

論理合成

ISEを用いた論理合成の結果、FPGA使用リソースは以下の様になりました。

| Logic Utilization | |

|---|---|

| Number of Slice Flip Flops | 1,144 out of 7,168 15% |

| Number of 4 input LUTs | 1,871 out of 7,168 26% |

| Logic Distribution | |

| Number of occupied Slices | 1,268 out of 3,584 35% |

| Number of RAMB16s | 4 out of 16 25% |

*1 OpenCoresで推奨されているSoC用インターコネクト規格