Vivadoでビルドインのロジックアナライザを使ってデバッグする場合の手順です。

1. Vivadoのプロジェクトを準備する

デバッグを行うデザインを含むVivadoのプロジェクトを用意します。

2. HDLにマークをつける

デバッグを行う信号にマークを付けます。Verilogの場合は(* mark_debug = “true” *)です。次の例では、AXIマスタモジュールのポート宣言部分に(* mark_debug = “true” *)を追加しています。(Block Design内の信号を観測する場合の手順はこちら。)

// AXI Master // write port(デバッグ対象デザインのVerilogファイル) (* mark_debug = "true" *) output [P_AXI_M_AWID-1:0] o_awid_m; (* mark_debug = "true" *) output [P_AXI_M_AWADDR-1:0] o_awaddr_m; (* mark_debug = "true" *) output [P_AXI_M_AWLEN-1:0] o_awlen_m; (* mark_debug = "true" *) output [P_AXI_M_AWSIZE-1:0] o_awsize_m; (* mark_debug = "true" *) output [P_AXI_M_AWBURST-1:0] o_awburst_m; (* mark_debug = "true" *) output [P_AXI_M_AWLOCK-1:0] o_awlock_m; (* mark_debug = "true" *) output [P_AXI_M_AWCACHE-1:0] o_awcache_m; (* mark_debug = "true" *) output [P_AXI_M_AWUSER-1:0] o_awuser_m; (* mark_debug = "true" *) output [P_AXI_M_AWPROT-1:0] o_awprot_m; (* mark_debug = "true" *) output o_awvalid_m; (* mark_debug = "true" *) input i_awready_m; (* mark_debug = "true" *) output [P_AXI_M_WID-1:0] o_wid_m; (* mark_debug = "true" *) output [P_AXI_M_WDATA-1:0] o_wdata_m; (* mark_debug = "true" *) output [P_AXI_M_WSTRB-1:0] o_wstrb_m; (* mark_debug = "true" *) output o_wlast_m; (* mark_debug = "true" *) output o_wvalid_m; (* mark_debug = "true" *) input i_wready_m; (* mark_debug = "true" *) input [P_AXI_M_BID-1:0] i_bid_m; (* mark_debug = "true" *) input [P_AXI_M_BRESP-1:0] i_bresp_m; (* mark_debug = "true" *) input i_bvalid_m; (* mark_debug = "true" *) output o_bready_m;

3.論理合成

mark_debugを付けたHDLでVivadoの”Run Synthesis”を実行します。

4.デバッグのセットアップ

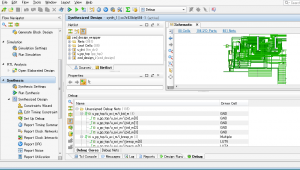

通常は”Run Implementation”に進むところですが、その前に”Open Synthesized Design”を実行します。

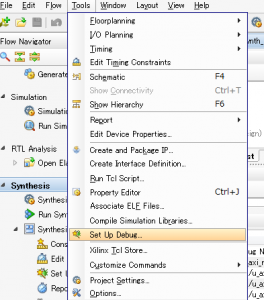

次にメニューからTools->Set Up Debug…を実行します。

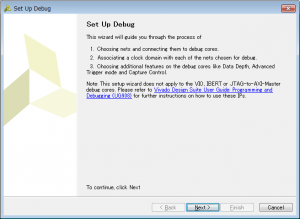

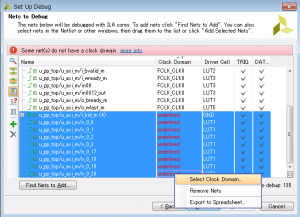

Set Up Debugウィンドウが現れます。Nextをクリックします。

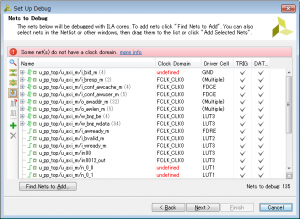

HDLでmark_debugを追加した信号が表示されます。ここで、論理合成時にクロックが推定できなかった信号は、Clock Domainがundefinedになります。例えば、固定信号などをmark_debugにするとundeginedになる場合があります。

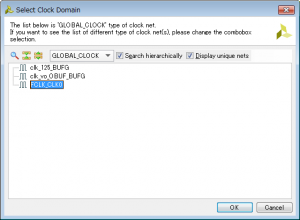

このような場合は、undefined部分を右クリックして、Select Clock Domainで明示的にクロックを指定します。

ここではFCLK_CLK0をundefinedに指定しています。

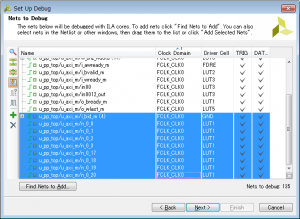

undefinedが消えます。Nextをクリックします。

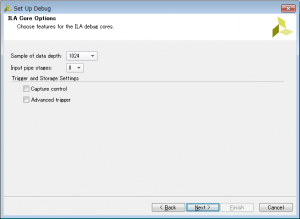

ロジックアナライザのオプションを指定します。サンプル数などを設定します。Nextをクリックします。

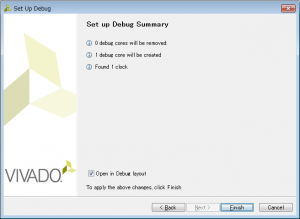

設定終了です。Finishをクリックします。

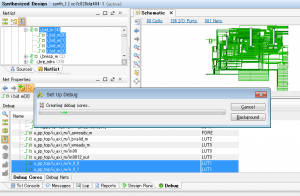

デバッグ用の追加データが自動的に生成されます。

5. Implementation実行とBitstream生成

通常の手順で”Run Implementation”と”Generate Bitstream”を実行します。

この時、制約条件ファイルの.xdcには次のようなデバッグに関する情報が追加されます。

create_debug_core u_ila_0 ila set_property ALL_PROBE_SAME_MU true [get_debug_cores u_ila_0] set_property ALL_PROBE_SAME_MU_CNT 1 [get_debug_cores u_ila_0] : :

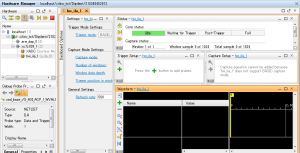

6. デバッグ画面の表示

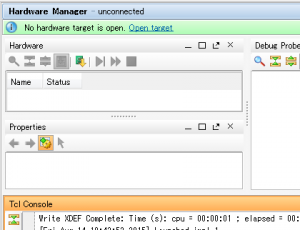

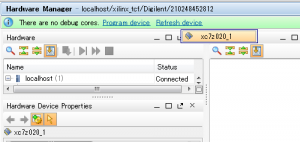

Hardware Managerを開き、”Open target”をクリックします。

Auto Connectをクリックします。

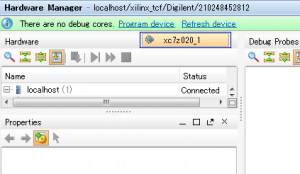

ターゲットが認識されるので、”Program device”でbitstreamをダウンロードします。

ZynqデバイスのFCLK_CLK0など、PSからのクロックをロジックアナライザに使用している場合は、Xilinx SDKでプログラムを実行してクロック供給を有効にします。その後、”Refresh device”を実行します。

デバッグ画面が表示されます。

7. デバッグ

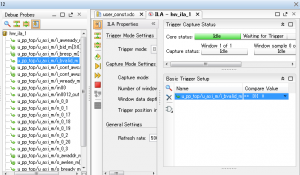

Debug Probesでトリガに使う信号を選び、ドラッグ&ドロップでBasic Trigger Setupに設定します。Compare Valueにはトリガ条件を指定します。

波形ウィンドウを表示するために、まずは適当にトリガーをかけます。

表示したい信号をDebug Probesで選択し、右クリックで表示されるAdd Probes to Waveformを実行します。

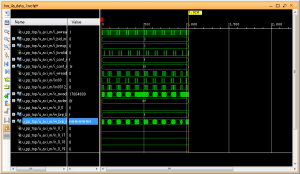

信号が波形表示されます。

まとめ

Vivadoのロジックアナライザはmark_debugで指定した信号名がそのまま表示されるので便利です。ISEのChipscopeだと自分で信号名を付けていたので不便でした。やっとQuartus IIのSignaTapIIと同じ感覚でデバッグできるようになりました。

追記

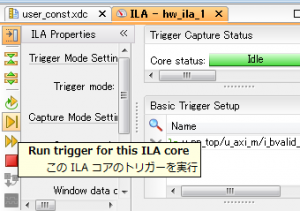

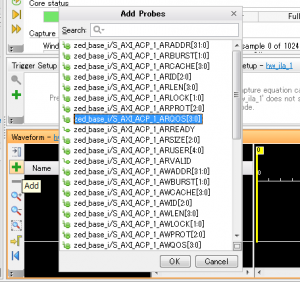

この記事で使用したVivadoのバージョンは2014.3だったのですが、新しいバージョンではロジックアナライザのユーザー・インターフェースが少し変わっているようです。例えば、Vivado 2015.4は次のようなユーザー・インターフェースになっています。

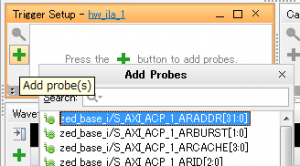

Debug Probesが見当たりませんが、Window->Debug Probesで表示できるようです。ただ、Waveformへの波形の追加はWavefromウィンドウのAddボタンから行えるので、Debug Probesは不要かもしれません。

同様に、トリガーの設定もTrigger SetupのAdd Probe(s)ボタンから簡単に行えるようです。