Verilogはdefineマクロなどを格納した別ファイルをインクルードできます。

`include "vlg_define.v" module top ( clk, rst_x, : ): :

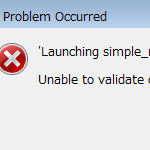

Quartus IIでこのようなVerilogファイルの論理合成を行う場合、どこかで`includeが参照するディレクトリを指定する必要があります。必要なインクルードファイルが見つからなかった場合、論理合成で次のようなエラーが発生します。

Error (10054): Verilog HDL File I/O error at top.v(1): can't open Verilog Design File "vlg_define.v"

Quartus IIのどこで指定するか

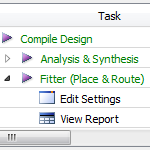

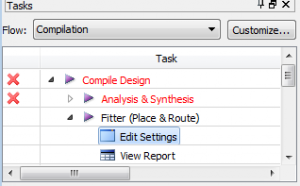

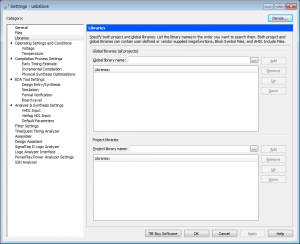

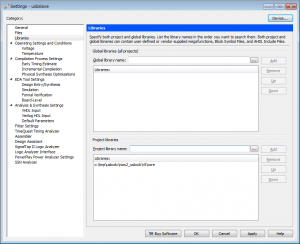

Edit Settingsをダブルクリックすると表示されるSettingsウィンドウのLibrariesカテゴリで設定します。

まず、Quartus IIでEdit Settingsをダブルクリックします。

SettingsウィンドウのLibrariesカテゴリを選択します。

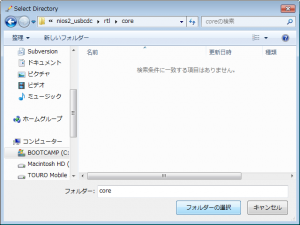

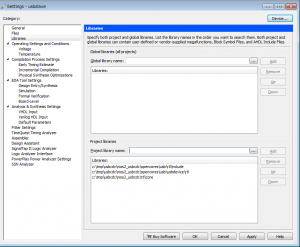

Project libraliesのProject libralies name:の右にある「…」の部分をクリックしてインクルードファイルが格納されているディレクトリを指定します。

Addボタンを押すと、ディレクトリが追加されます。

インクルードディレクトリが複数の場合、必要なだけこの処理を繰り返します。

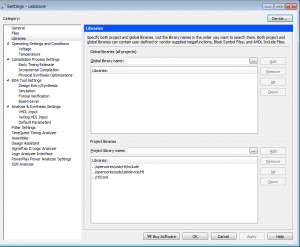

設定が終了したら、OKをクリックしてSettingsウィンドウを閉じます。

相対パスで設定する場合

Quartus IIの設定ファイル(.qsf)を直接編集する方法が簡単です。エディタなどで.qsfファイルを開き、SEARCH_PATHという文字列を検索すると、インクルードディレクトリの設定が見つかります。

set_global_assignment -name SEARCH_PATH "c:\\tmp\\usbcdc\\nios2_usbcdc\\opencores\\usb\\rtl\\include" set_global_assignment -name SEARCH_PATH "c:\\tmp\\usbcdc\\nios2_usbcdc\\opencores\\usb\\usbdevice\\rtl" set_global_assignment -name SEARCH_PATH "c:\\tmp\\usbcdc\\nios2_usbcdc\\rtl\\core"

この部分をプロジェクトディレクトリ(.qsfが存在するディレクトリ)からの相対パスに書きえます。この例の場合、nios2_usbcdcからの相対パスに書き換えると次のようになります。

set_global_assignment -name SEARCH_PATH "../opencores/usb/rtl/include" set_global_assignment -name SEARCH_PATH "../opencores/usb/usbdevice/rtl" set_global_assignment -name SEARCH_PATH "../rtl/core"

unixライクなパスの記述でもQuartus IIは認識するようです。

再度Quarus IIでプロジェクトを開いてLibraiesカテゴリで設定が反映されているか確認します。