ZedboardをSDカードからブートする方法のメモです。

用意するもの

既にUSB-JTAG経由で動作確認の終わっているVivadoプロジェクト。

作成手順

以下の手順はVivado 2014.3.1で確認しています。

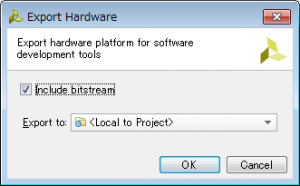

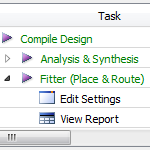

1. 最新のbitstreamの生成とエキスポート

Vivadoで作成済みのプロジェクトを開き、bitstreamの生成までを終了しておきます。次に

File->Export->Export Hardware …を実行します。この時、Include bitstreamにチェックを入れます。

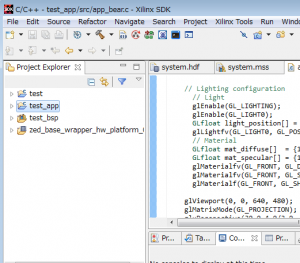

2. SDKの起動

File->Launch SDKでXilinx SDKを起動します。この例では、作成済みのプロジェクト”test_app”をSDカードからブートします。これ以降の処理はすべてXilinx SDKで行います。

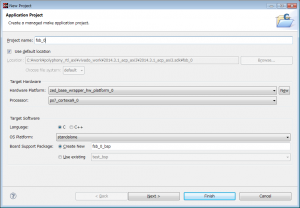

3. ブートローダープロジェクトの追加

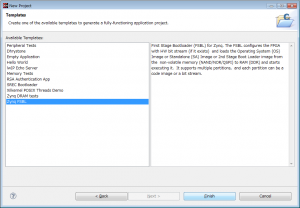

File->New->Application Projectで新しいプロジェクトを作成します。Project nameに適当な名前を入れてNext > をクリックします。この時、Board Support Packageは新しく作成した方がトラブルが少ないです。

Zynq FSBLを選択してFinishを実行します。FSBLは”First Stage Bootloader”の略です。

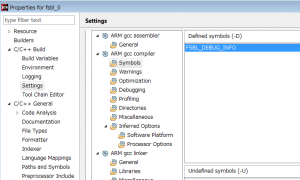

4. デバッグオプションの設定

FSBLでデバッグ情報を表示するように設定します。具体的には、C/C++ BuildのSettings ARM gcc compilerのSymbolsにFSBL_DEBUG_INFOを追加します。これを設定すると、ブート時にシリアルコンソールで起動プロセスを確認できるようになります。

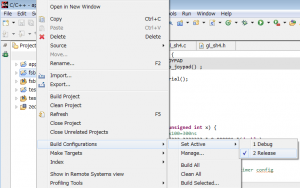

5. FSBLのコンパイル

FSBLのコンフィギュレーションを設定します。具体的には、プロジェクトをマウスで右クリックしてBuild Configurations->Set Active->2. Releaseを選択します。その後、Build Projectでプロジェクトをコンパイルします。

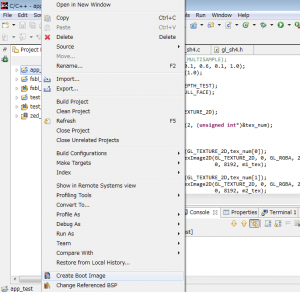

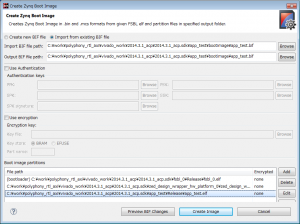

6. Create Zynq Boot Imageの起動

ブート対象のアプリケーションプロジェクトを選択し、マウスの右クリックでCreate Boot Imageを実行します

7. ブートデータの生成

Import from existing BIF fileが選択され、ブートに必要なデータが自動的に認識されているはずです。この例ではBoot image partitionsにfsbl_0.elf, zed_design_wrapper.bit, app_test.elfが認識されています。

Crate Imageをクリックすると、アプリケーションプロジェクトのディレクトリにBOOT.binが生成されます(この例の場合、app_test\bootimage\BOOT.bin)。

これで、ブートデータの生成は終了です。

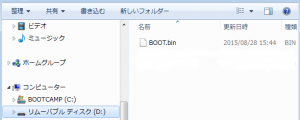

SDカードの準備

SDカードをFAT32で初期化します。

次に、生成したBOOT.binをSDカードのroot直下にコピーします。

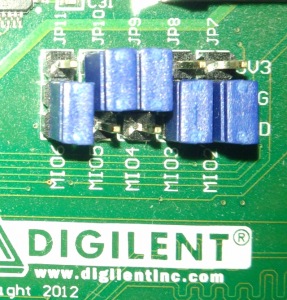

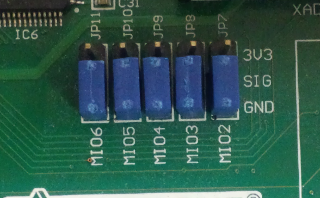

Zedboardの設定

ZedboardのジャンパをSDカードから起動するように変更します。具体的には、JP7 – JP11を次のように設定します。

(SDカードからの起動をやめて、JTAGから起動する場合はジャンパの設定を元に戻します。)

電源ON

あとはZedboardにSDカードを挿入して電源をONにするだけです。

この時、シリアルコンソールを接続すればブートプロセスが確認できます。SDカードの種類によっては、ブートに失敗する場合がありました。その場合のログが以下です。

Xilinx First Stage Boot Loader Release 2014.3 Aug 28 2015-13:46:54 Devcfg driver initialized Silicon Version 1.0 Boot mode is SD SD: rc= 0 SD: Unable to open file BOOT.BIN: 1 SD_INIT_FAIL FSBL Status = 0xA009 This Boot Mode Doesn't Support Fallback In FsblHookFallback function

SDカードを別のものに取り換えると、正常に動作しました。

Xilinx First Stage Boot Loader Release 2014.3 Aug 28 2015-13:46:54 Devcfg driver initialized Silicon Version 1.0 Boot mode is SD SD: rc= 0 SD Init Done Flash Base Address: 0xE0100000 Reboot status register: 0x60008201 Image Start Address: 0x00000000 Partition Header Offset:0x00000C80 Partition Count: 4 Partition Number: 1 Header Dump Image Word Len: 0x000F6EC0 Data Word Len: 0x000F6EC0 Partition Word Len:0x000F6EC0 Load Addr: 0x00000000 Exec Addr: 0x00000000 Partition Start: 0x000065D0 Partition Attr: 0x00000020 Partition Checksum Offset: 0x00000000 Section Count: 0x00000001 Checksum: 0xFFD14B7E Bitstream In FsblHookBeforeBitstreamDload function PCAP:StatusReg = 0x40000A30 PCAP:device ready PCAP:Clear done Level Shifter Value = 0xA Devcfg Status register = 0x40000A30 PCAP:Fabric is Initialized done PCAP register dump: PCAP CTRL 0xF8007000: 0x4C00607F PCAP LOCK 0xF8007004: 0x00000002 PCAP CONFIG 0xF8007008: 0x00000508 PCAP ISR 0xF800700C: 0x0802000B PCAP IMR 0xF8007010: 0xFFFFFFFF PCAP STATUS 0xF8007014: 0x00003A30 PCAP DMA SRC ADDR 0xF8007018: 0x00100001 PCAP DMA DEST ADDR 0xF800701C: 0xFFFFFFFF PCAP DMA SRC LEN 0xF8007020: 0x000F6EC0 PCAP DMA DEST LEN 0xF8007024: 0x000F6EC0 PCAP ROM SHADOW CTRL 0xF8007028: 0xFFFFFFFF PCAP MBOOT 0xF800702C: 0x00000000 PCAP SW ID 0xF8007030: 0x00000000 PCAP UNLOCK 0xF8007034: 0x757BDF0D PCAP MCTRL 0xF8007080: 0x00000000 DMA Done ! FPGA Done ! In FsblHookAfterBitstreamDload function Partition Number: 2 Header Dump Image Word Len: 0x00000002 Data Word Len: 0x00000002 Partition Word Len:0x00000002 Load Addr: 0x00230000 Exec Addr: 0x00100000 Partition Start: 0x000FD490 Partition Attr: 0x00000010 Partition Checksum Offset: 0x00000000 Section Count: 0x00000002 Checksum: 0xFFBD28F7 Application Partition Number: 3 Header Dump Image Word Len: 0x0004C005 Data Word Len: 0x0004C005 Partition Word Len:0x0004C005 Load Addr: 0x00100000 Exec Addr: 0x00000000 Partition Start: 0x000FD4A0 Partition Attr: 0x00000010 Partition Checksum Offset: 0x00000000 Section Count: 0x00000000 Checksum: 0xFFD1E8E0 Application Handoff Address: 0x00100000 In FsblHookBeforeHandoff function SUCCESSFUL_HANDOFF FSBL Status = 0x1