Mac OS X YosemiteにIcarus Verilogをインストールしました。Icarus Verilogはオープンソース(GNU General Public License)のVerilogシミュレータです。

インストール手順は次の2ステップです。

1. autoconfのインストール

2. Icarus Verilogソースコードの入手とコンパイル

インストールの手順はLinuxの場合と基本的に同じです。

1. autoconfのインストール

Icarus Verilogのコンパイルにはautoconfが必要ですが、OS X Yosemiteにはインストールされていないようです。このため、最初にautoconfをインストールします。

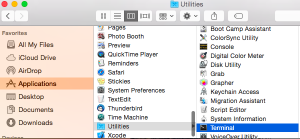

まず、Applications->Utilitiesからターミナルを開きます。

ターミナルから次の手順でauroconfをインストールします。

$mkdir temp $cd temp $curl -OL http://ftpmirror.gnu.org/autoconf/autoconf-2.68.tar.gz $tar xvzf autoconf-2.68.tar.gz $cd autoconf-2.68 $./configure $make $sudo make install

2. Icarus Verilogソースコードの入手とコンパイル

ソースコードの入手

適当なディレクトリでgitを使ってIcarus Verilogのソースコードを入手します。

$git clone git://github.com/steveicarus/iverilog.git

コンパイル

iverilogディレクトリに移動してautoconfを実行後、congiureとmakeを実行します。

$cd iverilog $autoconf $./configure $make

テストとインストール

make checkで動作確認後、make installでインストールします。

$make check (途中経過省略) : test -r check.conf || cp ./check.conf . driver/iverilog -B. -BPivlpp -tcheck -ocheck.vvp ./examples/hello.vl vvp/vvp -M- -M./vpi ./check.vvp | grep 'Hello, World' Hello, World

make installを行うと、デフォルトの設定では/usr/local/binに実行ファイルがインストールされます。

$sudo make install (途中経過省略) : ./../mkinstalldirs "/usr/local/bin" "/usr/local/lib/ivl" /usr/bin/install -c ./sizer.tgt "/usr/local/lib/ivl/sizer.tgt" ./../mkinstalldirs "/usr/local/bin" "/usr/local/share/man/man1" /usr/bin/install -c ./iverilog "/usr/local/bin/iverilog" /usr/bin/install -c -m 644 iverilog.man "/usr/local/share/man/man1/iverilog.1"

簡単な使い方

Icarus VerilogのQUICK_START.txtに記載されている通り、iverilogというプログラムを使ってVerilogファイルをコンパイルし、その結果をvvpというプログラムに渡すとシミュレーションが始まります。iverilogのオプション詳細は、ターミナルで”man iverilog”と入力すると表示されます。

Icarus Verilogのシミュレーションサンプルは、必要なVerilogファイルをコマンドファイルに列挙したものが多く見られますが、他のシミュレータと同様に-yオプションでモジュールのサーチパスを指定することも可能です。

次の例では、トップモジュール(テストベンチ)以外はVerilogファイルを指定していません。コマンドファイルには拡張子指定の最低限のコマンドのみ記述しています。(この例のサンプルはこちら)

#!/bin/sh

# RTL directory

RTL_DIR="../rtl"

TOP_MODULE=test_module

sim_file=$1

echo "Test Scenario=" $sim_file

# compile

iverilog -c ../bin/cmd.txt \

-y ${RTL_DIR} \

-o ${TOP_MODULE} \

${sim_file}

# simulation

vvp ${TOP_MODULE}

コマンドファイル(cmd.txt)の内容

+libext+.v

シミュレーション実行ログ

$../bin/run_iv.sh ../scenario/test_1.v Test Scenario= ../scenario/test_1.v Hello Icarus Verilog!! VCD info: dumpfile dump.vcd opened for output. Input Data: 24 Input Data: 81 Input Data: 09 Input Data: 63 Input Data: 0d Input Data: 8d Input Data: 65 Input Data: 12 Input Data: 01 Input Data: 0d

Icarus VerilogでVPIを使う場合の手順はこちら