Zynq-7000とCyclone Vの仕様書を読むと、2つのデバイスはかなり似ています。どちらのデバイスも、内部構成を単純化すると、次の図のようになっています。

内部構成

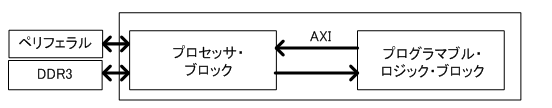

具体的には、次のような共通点があります。

- Cortex-A9x2を内蔵した、プロセッサ・ブロックがある。

- プログラマブル・ロジックのブロックがある。

- メイン・メモリはDDR3。

- ペリフェラル(USBやネットワーク)、メイン・メモリはプロセッサ・ブロックに接続されている。

プロセッサ・ブロックやプログラマブル・ロジック・ブロックは、実際にはそれぞれのデバイスで固有の名称がつけられています。

アドレス・マップの違い

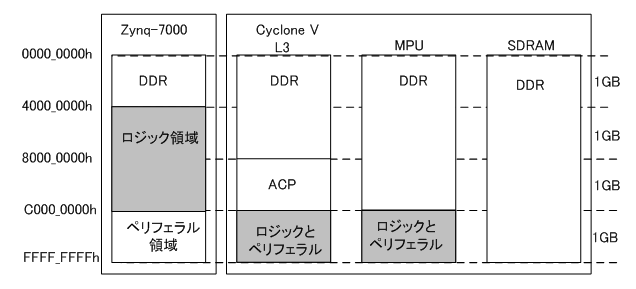

Zynq-7000とCyclone Vのアドレス・マップを比較すると、次のようになっています。

アドレス・マップの比較

Cyclone Vでは、マスタごとにアドレス・マップが分かれています(L3, MPU, SDRAM)。Zynq-7000も仕様書ではマスタごとにもう少し詳細な記述があるのですが、Cyclone Vほど大きな違いがないので、図では簡略化しています。アドレス・マップについて、具体的な違いは次のとおりです。

リニアにアクセス可能なDDR3領域

Cyclone Vは、アドレス・マップをアクセスするマスタの種類に応じて3種類のマップを使い分けます*。3種類のアドレス・マップでは、それぞれリニアにアクセスできるDDR3の領域が異なります。具体的には、L3と呼ばれるインターコネクトに接続されるマスタ(主にプログラマブル・ロジックに実装したユーザー回路)がリニアにアクセスできるのは2GB、MPU(Cortex-A9)は3GB、プログラマブル・ロジックからDDR3を直接アクセスする場合には4GBとなっています。一方、Zynq-7000ではリニアにアクセス可能なDDR3領域は1GBとなっています。

*Zynq-7000も仕様書ではマスタごとにマップがわかれているが、DDR3領域は1GBに固定されている。

リニアにアクセス可能なロジック領域

Zynq-7000は、2GBの領域がプログラマブル・ロジック領域に確保されています(正確には1GBx2)。一方、Cyclone Vは962MBです(正確には960MB+2MB)。

ACP(Accelerator Coherency Port)のマッピング

ACP機能のマッピングが異なります。ACPは、Cortex-A9のキャッシュの状態を意識することなくメイン・メモリをアクセスできる機能です。プログラマブル・ロジック側から見た場合、Cyclone Vでは8000_0000hからの1GBがACP領域に割り当てられています。具体的には、8000_0000hのオフセットを付加してDDR3をアクセスします。一方、Zynq-7000の場合は、Cyclone Vのようなオフセットは必要ありません。どちらのデバイスも、ACPを有効にするにはAXI信号等の設定が必要になります。それぞれのデバイスの仕様書によると、次の条件でACPが有効になるようです。

Zynq-7000

- リード時はARUSER[0] = 1かつARCACHE[1] = 1という条件が必要

- ライト時はAWUSER[0] = 1かつAWCACHE[1] = 1という条件が必要

Cyclone V

- リード時はARCACHEのアトリビュートがMMUページ・テーブルのアトリビュートと一致すること

- リード時はARUSER[0] = 1かつARCACHE[1] = 1という条件が必要

- ライト時はAWCACHEのアトリビュートがMMUページ・テーブルのアトリビュートと一致すること

- ライト時はAWUSER[0] = 1かつAWCACHE[1] = 1という条件が必要

- Cortex-A9 MPCoreは次の設定が必要

- Snoop Control Unitを有効にする

- コヒーレント・メモリはCacheable/Shareableに設定する

- ACTLRレジスタのSMPビットをセットする。

仕様書の記述レベルが違うだけで、実際にはどちらもほぼ同様の設定が必要なのかも知れません。

まとめ

アドレス・マップで一番大きな領域を占めているのは、Zynq-7000ではプログラマブル・ロジック、Cyclone VではDDR3メイン・メモリです。また、ACPについては、プログラマブル・ロジック側から見るとCyclone Vではアドレスがオフセットされているのに対し、Zynq-7000ではアドレスのオフセットなしです。このような設計思想の違いが興味深い所です。

こちらの資料には、Altera SoC FPGAとXilinx Zynq-7000 EPPのACPの違いがまとめられています。

https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ab/ab07_soc_fpga.pdf