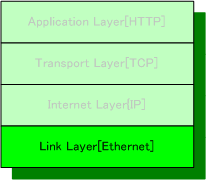

Internet Protocol Suite

OpenCores

This implementation uses an open source IP core “Ethernet IP Core” as Ethernet MAC sub Layer. Ethernet IP Core is freely available from OpenCores*1.

Stand-Alone Testing

Before implementing the IP Core in the system, check the basic function in the stand-alone environment to avoid implementing issue. The Core is tested under the following environment.

- OS: Windows XP Cygwin

- Verilog simulator: GPL Cver*2

Download the archive data from the web site, then extract the data in a work directory.

$tar xvzf ethmac_latest.tar.gz

The following directories are extracted from the archive data. The implementation for this project uses data in trunk directory version.

branches tags trunk web_uploads trunk: README.txt bench doc rtl sim

To simplify the option setting of the verilog simulator, file name is modified if the file name and module name defined in the file is not same.

cd bench/verilog mv wb_master_behavioral.v WB_MASTER_BEHAVIORAL.v mv wb_slave_behavioral.v WB_SLAVE_BEHAVIORAL.v mv wb_bus_mon.v WB_BUS_MON.v mv wb_master32.v WB_MASTER32.v cd ../..

Make working directories under trunk for .GPL Cver simulation.

mkdir work cd work mkdir log mkdir sim

Put the following simulation script into work/sim directory as a file named “run_cver.sh”.

(work/sim/run_cver.sh)

#!/bin/csh -f

# cver simulation script

set RTL_DIR = "../../rtl/verilog"

set BENCH_DIR = "../../bench/verilog"

set XILINX_DIR = "C:\Xilinx\10.1\ISE\verilog\src"

cver \

+notimingchecks \

-y . \

-y ${RTL_DIR} \

-y ${BENCH_DIR} \

-y ${XILINX_DIR} \

-y ${XILINX_DIR}/unisims \

+incdir+${RTL_DIR}/+ \

+incdir+${BENCH_DIR}+ \

+libext+.v+ \

../../bench/verilog/tb_ethernet.v

Run the simulation scrip t(run_cver.sh) in work/sim. The simulation starts from MII access tests between MAC and PHY, then continues to Ethernet Frame transfer tests..

(Execution Log)

GPLCVER_2.12a of 05/16/07 (Cygwin32). Copyright (c) 1991-2007 Pragmatic C Software Corp. All Rights reserved. Licensed under the GNU General Public License (GPL). See the 'COPYING' file for details. NO WARRANTY provided. Today is Thu Aug 20 21:07:55 2009. Compiling source file "../../bench/verilog/tb_ethernet.v" Highest level modules: tb_ethernet ACCESS TO MAC REGISTERS TEST Time: 62387 TEST 0: BYTE SELECTS ON 3 32-BIT READ-WRITE REGISTERS ( VARIOUS BUS DELAYS ) Time: 68509 TEST 1: 'WALKING ONE' WITH SINGLE CYCLES ACROSS MAC REGISTERS ( VARIOUS BUS D LAYS ) ->registers tested with 0, 1, 2, 3 and 4 bus delay cycles Time: 302749 TEST 2: 'WALKING ONE' WITH SINGLE CYCLES ACROSS MAC BUFFER DESC. ( VARIOUS BUS DELAYS ) ->buffer descriptors tested with 0 bus delay ->buffer descriptors tested with 1 bus delay cycle ->buffer descriptors tested with 2 bus delay cycles ->buffer descriptors tested with 3 bus delay cycles Time: 5383309 TEST 3: MAX REG. VALUES AND REG. VALUES AFTER WRITING INVERSE RESET VALUES AND HARD RESET OF THE MAC Time: 5399539 TEST 4: BUFFER DESC. RAM PRESERVING VALUES AFTER HARD RESET OF THE MAC AND RESETING THE LOGIC MIIM MODULE TEST Time: 5645717 TEST 0: CLOCK DIVIDER OF MII MANAGEMENT MODULE WITH ALL POSSIBLE FREQUENCES Time: 7595117 TEST 1: VARIOUS READINGS FROM 'REAL' PHY REGISTERS Time: 7622149 TEST 2: VARIOUS WRITINGS TO 'REAL' PHY REGISTERS ( CONTROL AND NON WRITABLE REGISTERS ) Time: 7655119 TEST 3: RESET PHY THROUGH MII MANAGEMENT MODULE Time: 7673959 TEST 4: 'WALKING ONE' ACROSS PHY ADDRESS ( WITH AND WITHOUT PREAMBLE ) Time: 7749859 TEST 5: 'WALKING ONE' ACROSS PHY'S REGISTER ADDRESS ( WITH AND WITHOUT PREAMBLE ) Time: 7825759 TEST 6: 'WALKING ONE' ACROSS PHY'S DATA ( WITH AND WITHOUT PREAMBLE ) Time: 8067259 TEST 7: READING FROM PHY WITH WRONG PHY ADDRESS ( HOST READING HIGH 'Z' DATA ) => Two error lines will be displayed from WB Bus Monitor, because correct HIGH Z data was read Time: 8071935 tb_ethernet.wb_eth_slave_bus_mon.message_out, Slave provided invalid data during read and qualified it with ACK_I Byte select value: SEL_O = 1111, Data bus value: DAT_I = 0000zzzz Time: 8071969 TEST 8: WRITING TO PHY WITH WRONG PHY ADDRESS AND READING FROM CORRECT ONE Time: 8081389 TEST 9: SLIDING STOP SCAN COMMAND IMMEDIATELY AFTER READ REQUEST ( WITH AND WITHOUT PREAMBLE ) Time: 8976619 TEST 10: SLIDING STOP SCAN COMMAND IMMEDIATELY AFTER WRITE REQUEST ( WITH AND WITHOUT PREAMBLE ) Time: 9882439 TEST 11: BUSY AND NVALID STATUS DURATIONS DURING WRITE ( WITH AND WITHOUT PREAMBLE ) Time: 10098649 TEST 12: BUSY AND NVALID STATUS DURATIONS DURING READ ( WITH AND WITHOUT PREAMBLE ) Time: 10315609 TEST 13: BUSY AND NVALID STATUS DURATIONS DURING SCAN ( WITH AND WITHOUT PREAMBLE ) Time: 10532569 TEST 14: SCAN STATUS FROM PHY WITH DETECTING LINK-FAIL BIT ( WITH AND WITHOUT PREAMBLE ) Time: 10676539 =========================================================================== PHY generates ideal Carrier sense and Collision signals for following tests =========================================================================== MAC FULL DUPLEX TRANSMIT TEST Time: 14603687 TEST 0: NO TRANSMIT WHEN ALL BUFFERS ARE RX ( 10Mbps ) Time: 15301879 TEST 1: NO TRANSMIT WHEN ALL BUFFERS ARE RX ( 100Mbps ) Time: 15936319 TEST 2: TRANSMIT PACKETS FROM MINFL TO MAXFL SIZES AT ONE TX BD ( 10Mbps ) pads appending to packets is NOT selected ->packets with lengths from 64 (MINFL) to 128 are checked (length increasing by 1 byte) pads appending to packets is selected ->packets with lengths from 256 to 1408 are checked (length increasing by 128 bytes) pads appending to packets is NOT selected ->packets with lengths from 1516 to 1536 (MAXFL) are checked (length increasing by 1 byte) Time: 49726759 TEST 3: TRANSMIT PACKETS FROM MINFL TO MAXFL SIZES AT ONE TX BD ( 100Mbps )